**TU60 DECassette

tape transport

maintenance manual**

**DEC-00-HTU60-C-D**

**digital equipment corporation • maynard, massachusetts**

1st Edition December 1972

2nd Printing (Rev) April 1973

3rd Printing (Rev) October 1973

Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

|           |              |

|-----------|--------------|

| DEC       | PDP          |

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

## CONTENTS

|                                        | Page                                           |     |

|----------------------------------------|------------------------------------------------|-----|

| <b>CHAPTER 1 GENERAL INFORMATION</b>   |                                                |     |

| 1.1                                    | INTRODUCTION . . . . .                         | 1-1 |

| 1.2                                    | CASSETTE RESTRICTIONS . . . . .                | 1-1 |

| 1.3                                    | SPECIFICATIONS . . . . .                       | 1-2 |

| 1.4                                    | MAJOR ASSEMBLIES . . . . .                     | 1-5 |

| 1.4.1                                  | Controls and Indicators . . . . .              | 1-5 |

| 1.4.2                                  | Drive Mechanism . . . . .                      | 1-5 |

| 1.4.3                                  | Logic . . . . .                                | 1-8 |

| 1.4.4                                  | H751 Power Supply . . . . .                    | 1-8 |

| <b>CHAPTER 2 INSTALLATION</b>          |                                                |     |

| 2.1                                    | UNPACKING AND INSPECTION . . . . .             | 2-1 |

| 2.2                                    | ELECTRICAL INSTALLATION AND CHECKOUT . . . . . | 2-1 |

| 2.3                                    | OPERATION . . . . .                            | 2-3 |

| 2.3.1                                  | Cassette Loading and Unloading . . . . .       | 2-3 |

| 2.3.2                                  | Normal Operating Procedure . . . . .           | 2-4 |

| <b>CHAPTER 3 I/O INTERFACE SIGNALS</b> |                                                |     |

| 3.1                                    | INPUT INTERFACE SIGNALS . . . . .              | 3-1 |

| 3.1.1                                  | Select Enable L . . . . .                      | 3-1 |

| 3.1.2                                  | Drive B L . . . . .                            | 3-1 |

| 3.1.3                                  | Start L . . . . .                              | 3-1 |

| 3.1.4                                  | Rewind L . . . . .                             | 3-1 |

| 3.1.5                                  | Back Block Gap L . . . . .                     | 3-1 |

| 3.1.6                                  | Back File Gap L . . . . .                      | 3-1 |

| 3.1.7                                  | R/W File Gap L . . . . .                       | 3-2 |

| 3.1.8                                  | Write Mode L . . . . .                         | 3-2 |

| 3.1.9                                  | Transfer L . . . . .                           | 3-2 |

| 3.1.10                                 | R/W CRC L . . . . .                            | 3-2 |

| 3.1.11                                 | Initialize L . . . . .                         | 3-2 |

| 3.2                                    | OUTPUT INTERFACE SIGNALS . . . . .             | 3-2 |

| 3.2.1                                  | Off Line L . . . . .                           | 3-2 |

| 3.2.2                                  | Ready L . . . . .                              | 3-2 |

| 3.2.3                                  | End File L . . . . .                           | 3-3 |

| 3.2.4                                  | EOT/BOT L (End Tape) . . . . .                 | 3-3 |

| 3.2.5                                  | Rewind L . . . . .                             | 3-3 |

| 3.2.6                                  | Write Protect L . . . . .                      | 3-3 |

| 3.2.7                                  | Write Status L . . . . .                       | 3-3 |

| 3.2.8                                  | Transfer Req L . . . . .                       | 3-3 |

| 3.2.9                                  | Time Error L . . . . .                         | 3-3 |

| 3.2.10                                 | CRC Error L . . . . .                          | 3-3 |

| 3.2.11                                 | PWR OK L . . . . .                             | 3-3 |

| 3.2.12                                 | R/W Bits 1-8 (Bi-directional) . . . . .        | 3-3 |

## CONTENTS (Cont)

|                                                                         | <b>Page</b> |

|-------------------------------------------------------------------------|-------------|

| <b>CHAPTER 4      THEORY OF OPERATION</b>                               |             |

| 4.1 <b>GENERAL</b> . . . . .                                            | 4-1         |

| 4.2 <b>TAPE FORMAT AND MOTION CONTROL OPERATIONS</b> . . . . .          | 4-1         |

| 4.2.1              Manual Rewind . . . . .                              | 4-2         |

| 4.2.2              Programmed Rewind . . . . .                          | 4-2         |

| 4.2.3              Back Block Gap . . . . .                             | 4-2         |

| 4.2.4              Back File Gap . . . . .                              | 4-2         |

| 4.2.5              Forward File Gap . . . . .                           | 4-5         |

| 4.3 <b>READ/WRITE OPERATIONS</b> . . . . .                              | 4-5         |

| 4.3.1            Write File Gap . . . . .                               | 4-5         |

| 4.3.2            Write Data Block . . . . .                             | 4-5         |

| 4.3.3            Read Data Block/File . . . . .                         | 4-6         |

| 4.4 <b>PROGRAMMING RESTRICTIONS AND COMMAND TOPOLOGY</b> . . . . .      | 4-7         |

| 4.5 <b>DETAILED LOGIC DESCRIPTIONS</b> . . . . .                        | 4-7         |

| 4.5.1            Drive Selection . . . . .                              | 4-7         |

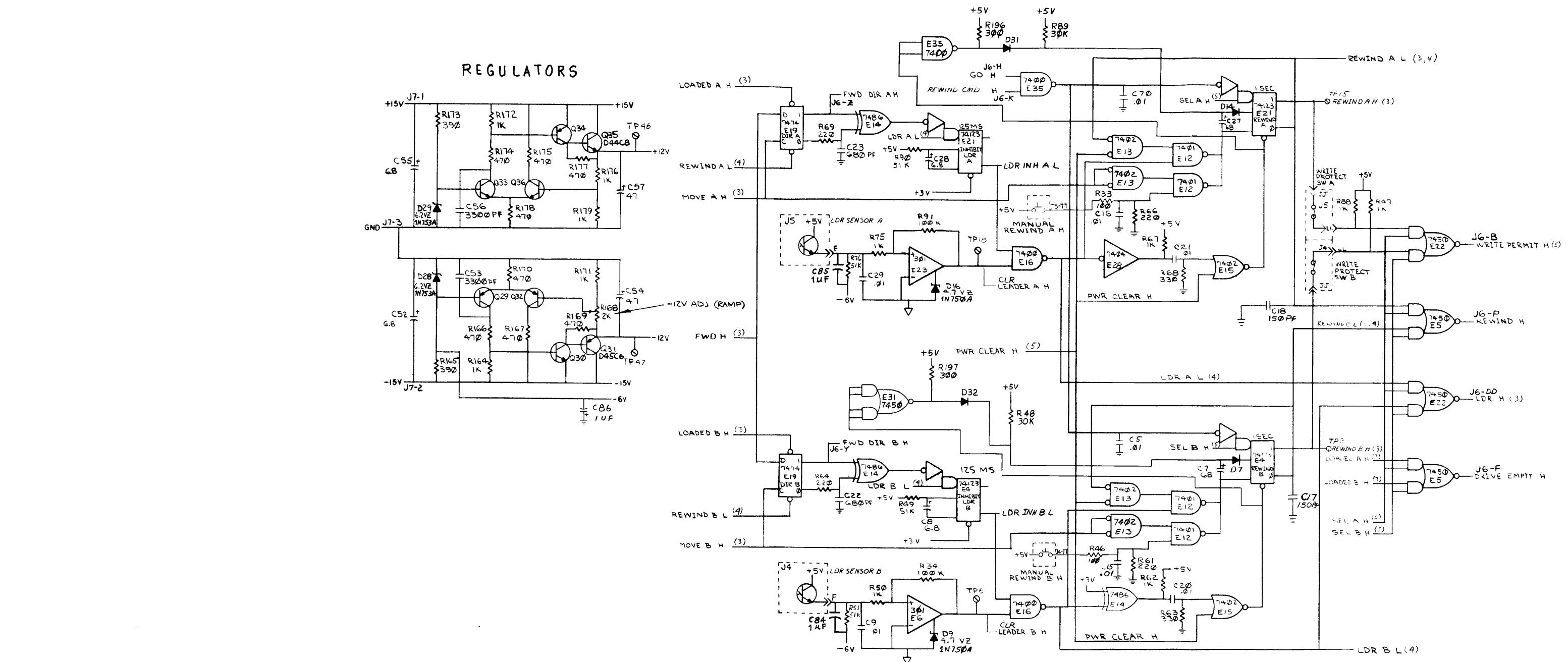

| 4.5.2            Rewind . . . . .                                       | 4-10        |

| 4.5.2.1      Manual Rewind . . . . .                                    | 4-10        |

| 4.5.2.2      Programmed Rewind . . . . .                                | 4-10        |

| 4.5.3          Back Block Gap . . . . .                                 | 4-11        |

| 4.5.4          Back File Gap . . . . .                                  | 4-12        |

| 4.5.5          Turn-Around Clear Leader Handling . . . . .              | 4-12        |

| 4.5.6          Forward File Gap . . . . .                               | 4-12        |

| 4.5.7          Write File Gap . . . . .                                 | 4-13        |

| 4.5.8          Write Data Block . . . . .                               | 4-14        |

| 4.5.8.1     Command Initiation . . . . .                                | 4-15        |

| 4.5.8.2     Tape Start and Pre Gap . . . . .                            | 4-15        |

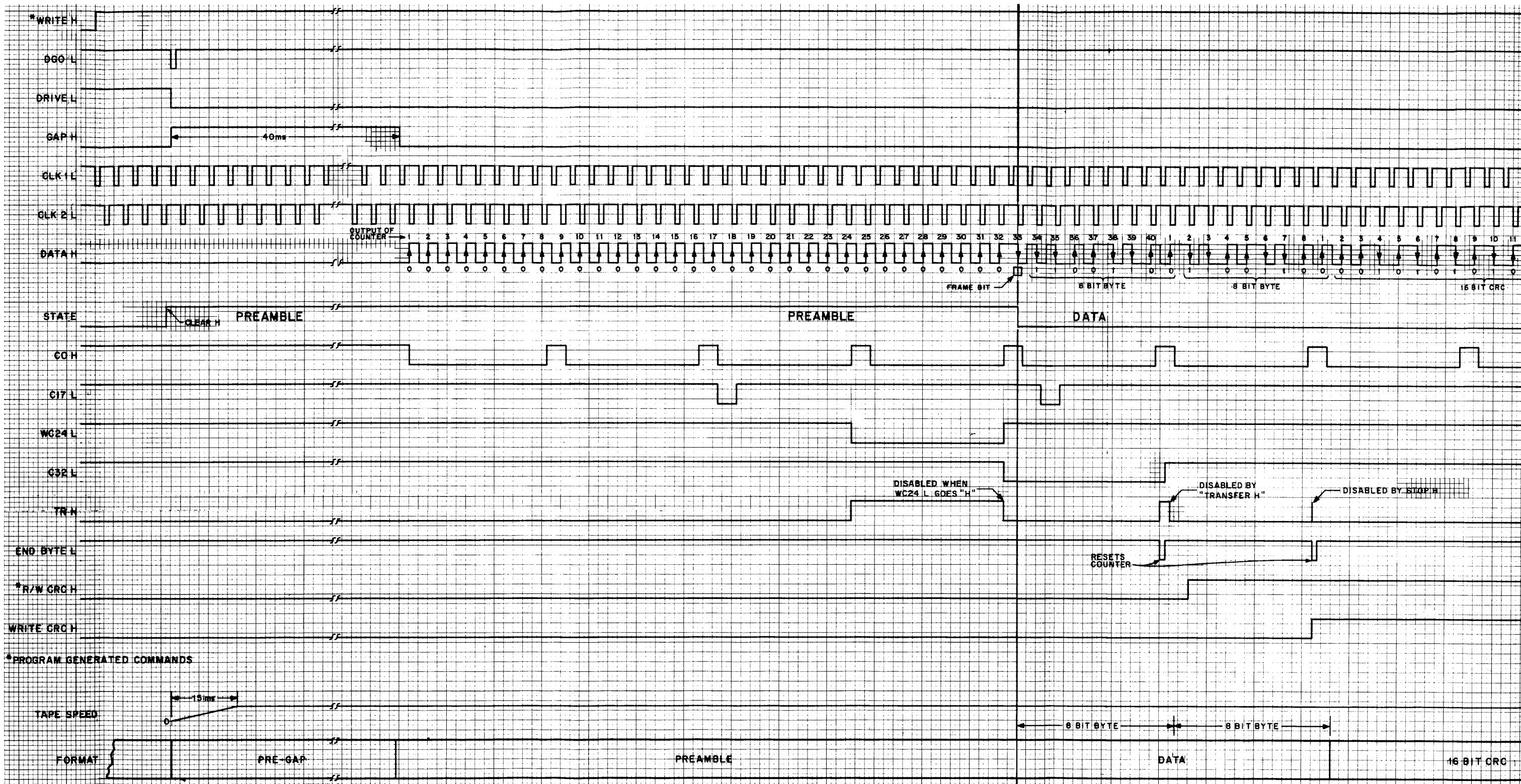

| 4.5.8.3     Write Preamble and Data Byte Transfer . . . . .             | 4-16        |

| 4.5.8.4     Write Data . . . . .                                        | 4-16        |

| 4.5.8.5     Write CRC Character . . . . .                               | 4-18        |

| 4.5.8.6     Post Gap and Tape Stop . . . . .                            | 4-18        |

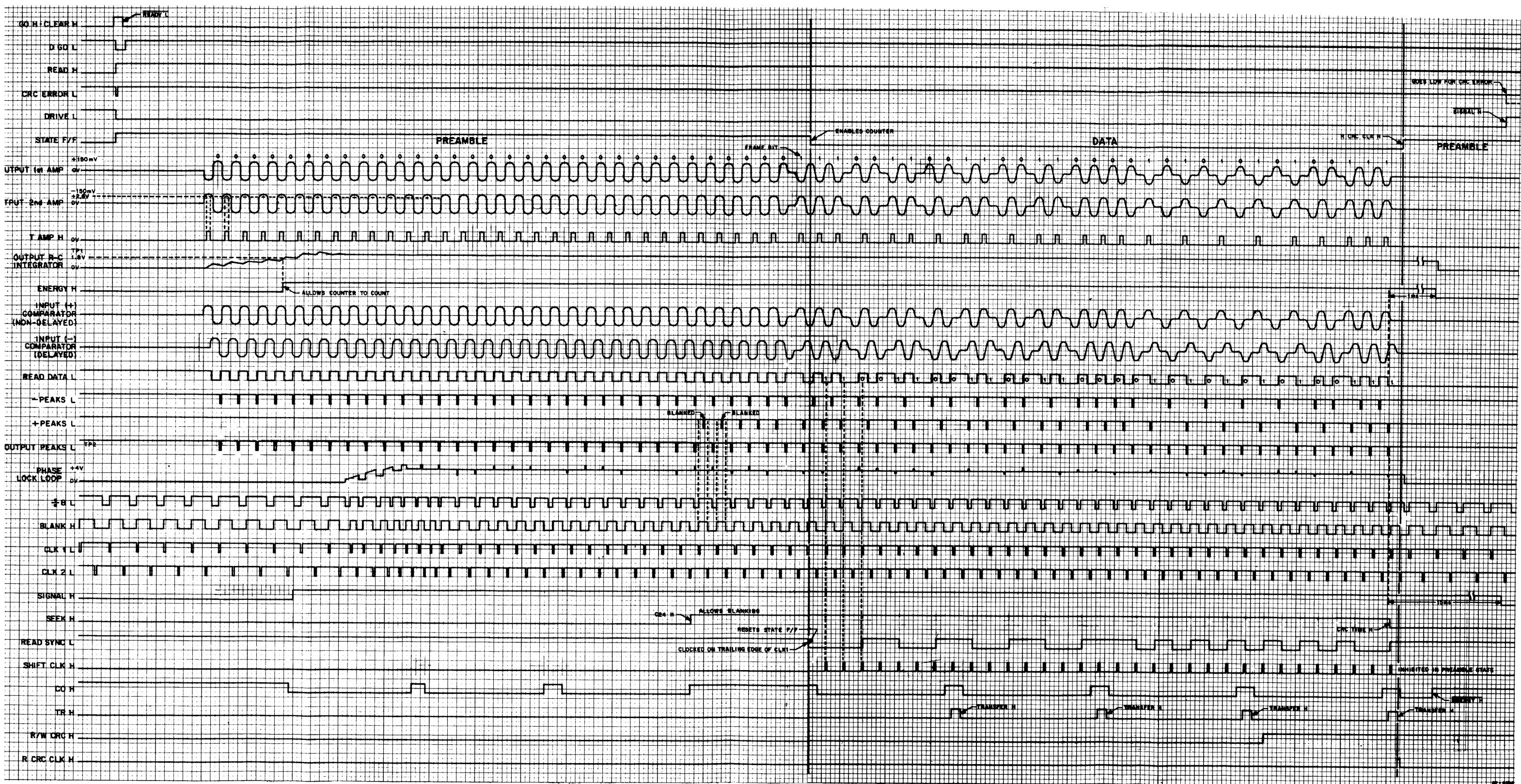

| 4.5.9          Read Data Block . . . . .                                | 4-18        |

| 4.5.9.1     Command Initiation . . . . .                                | 4-18        |

| 4.5.9.2     Tape Start and Pre Gap . . . . .                            | 4-18        |

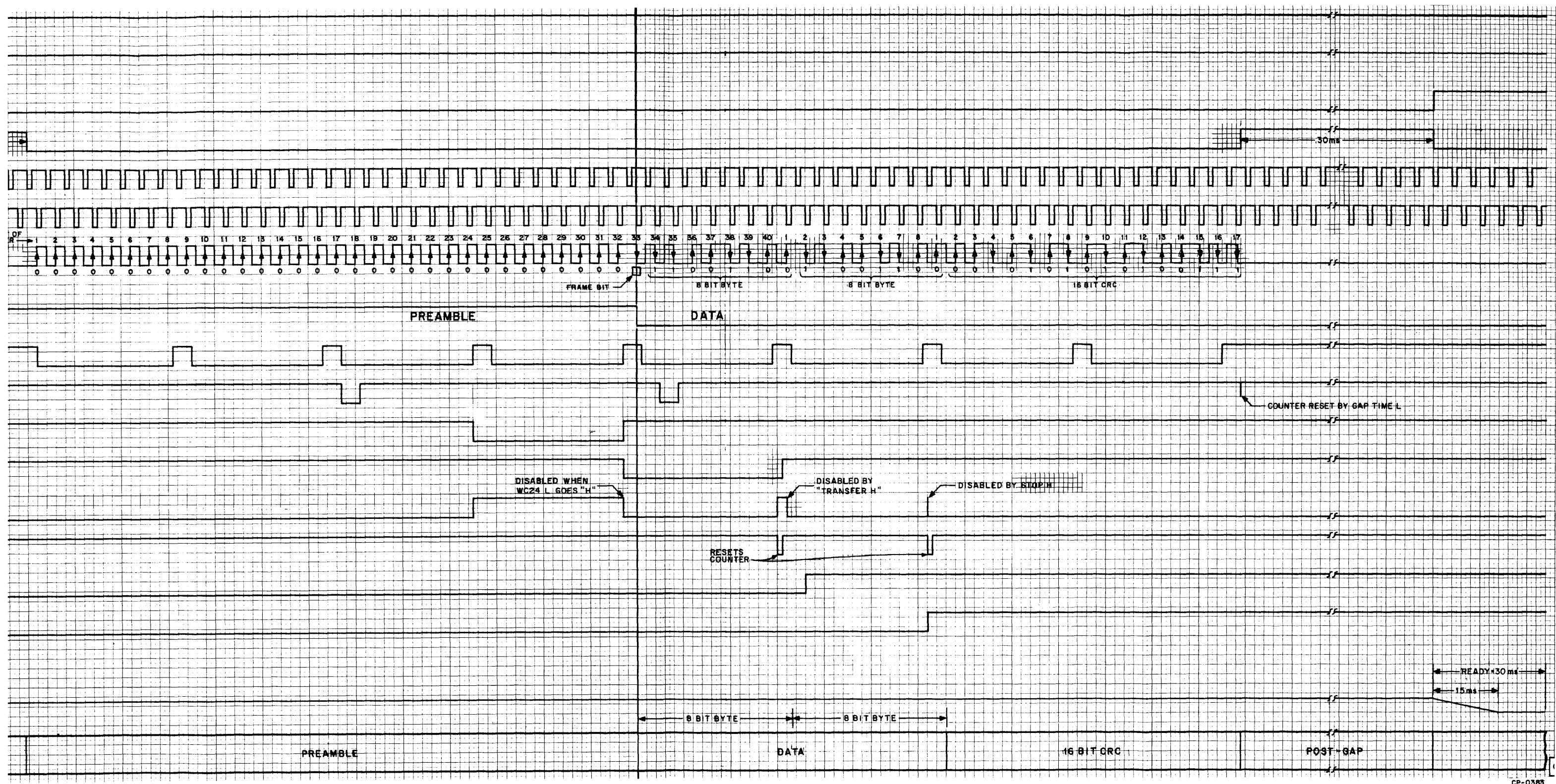

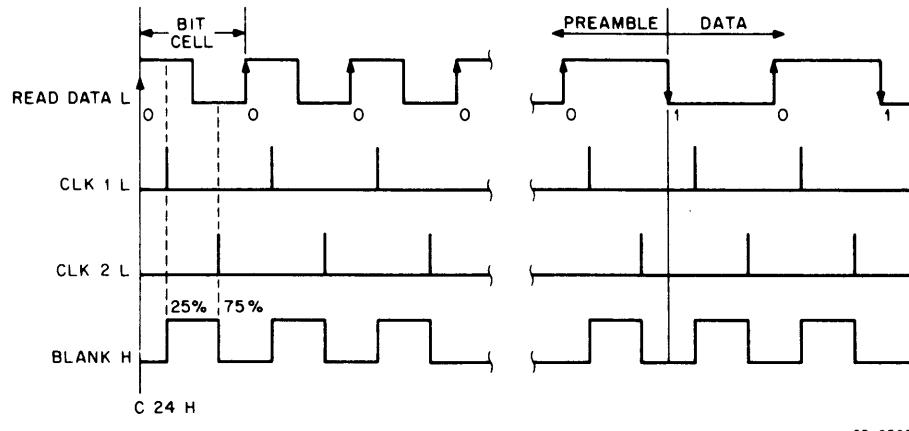

| 4.5.9.3     Preamble Detection and Read Clock Synchronization . . . . . | 4-19        |

| 4.5.9.4     End Preamble (Frame Bit Detection) . . . . .                | 4-19        |

| 4.5.9.5     Data Detection . . . . .                                    | 4-20        |

| 4.5.9.6     Read CRC Character . . . . .                                | 4-21        |

| 4.5.9.7     Tape Stop . . . . .                                         | 4-21        |

| 4.5.9.8     Tape Blank Stop . . . . .                                   | 4-21        |

| 4.5.10         CRC Character . . . . .                                  | 4-21        |

| 4.5.10.1    CRC Derivation . . . . .                                    | 4-22        |

| 4.5.10.2    CRC Validation . . . . .                                    | 4-22        |

| 4.5.11         Error and Logic Power Indications . . . . .              | 4-22        |

| 4.5.11.1    CRC Error . . . . .                                         | 4-22        |

| 4.5.11.2    Time Error . . . . .                                        | 4-22        |

| 4.5.11.3    Power OK . . . . .                                          | 4-23        |

## CONTENTS (Cont)

|                                                           | Page |

|-----------------------------------------------------------|------|

| 4.6 ANALOG CIRCUIT ANALYSIS . . . . .                     | 4-23 |

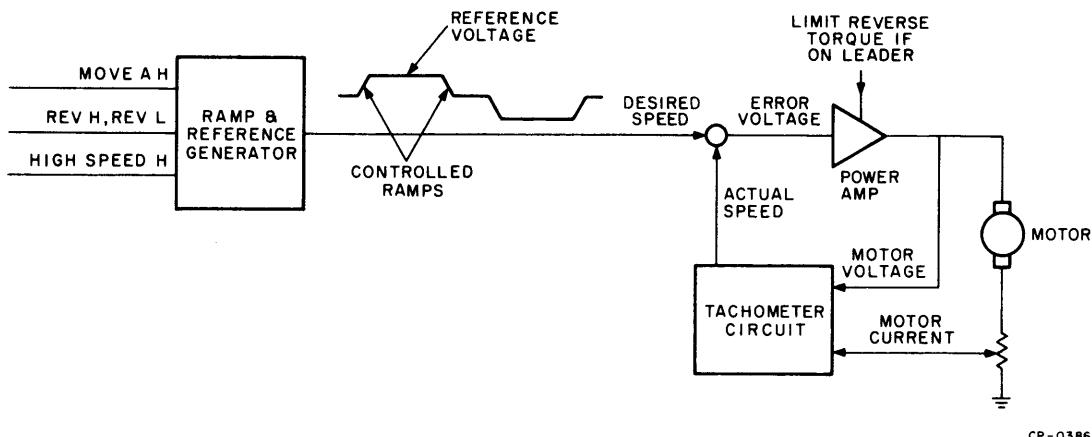

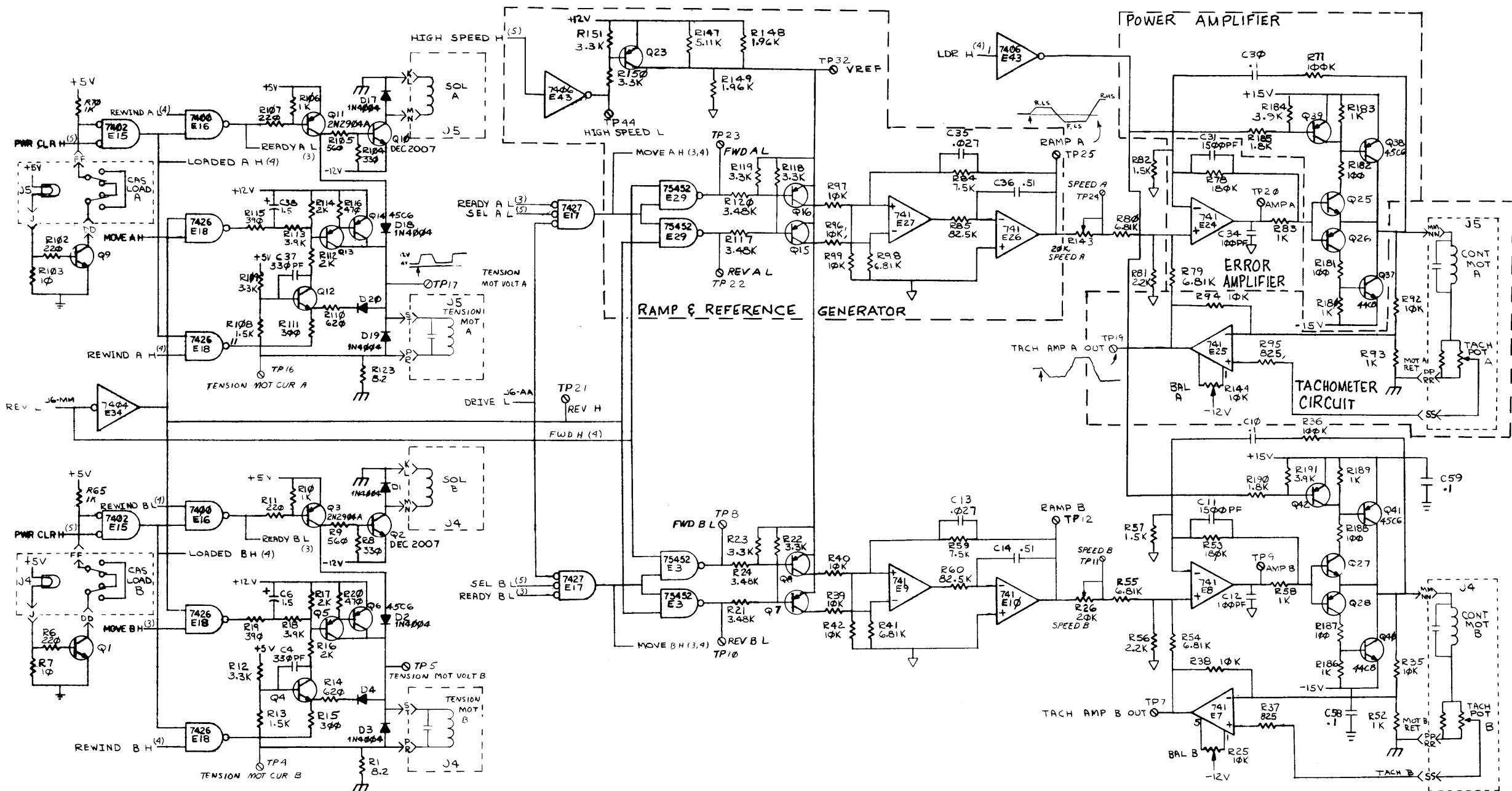

| 4.6.1 Control Motor Servo System . . . . .                | 4-23 |

| 4.6.1.1 Ramp and Reference Generator . . . . .            | 4-24 |

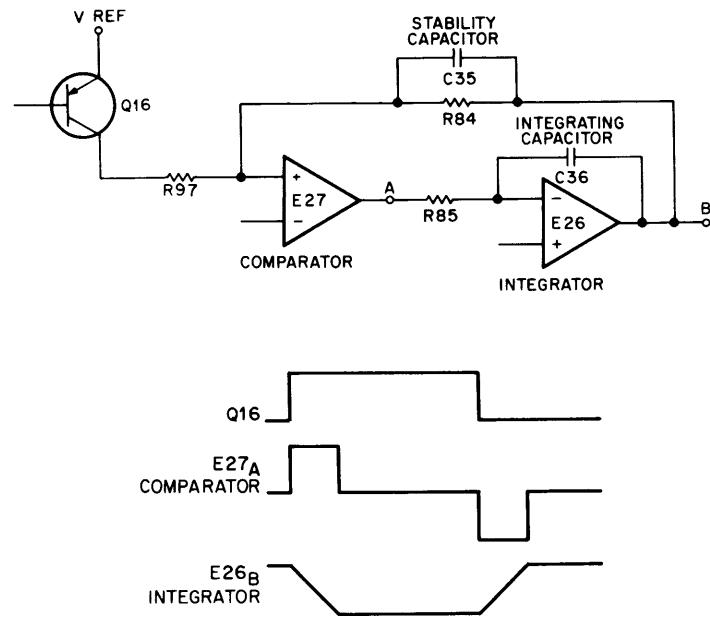

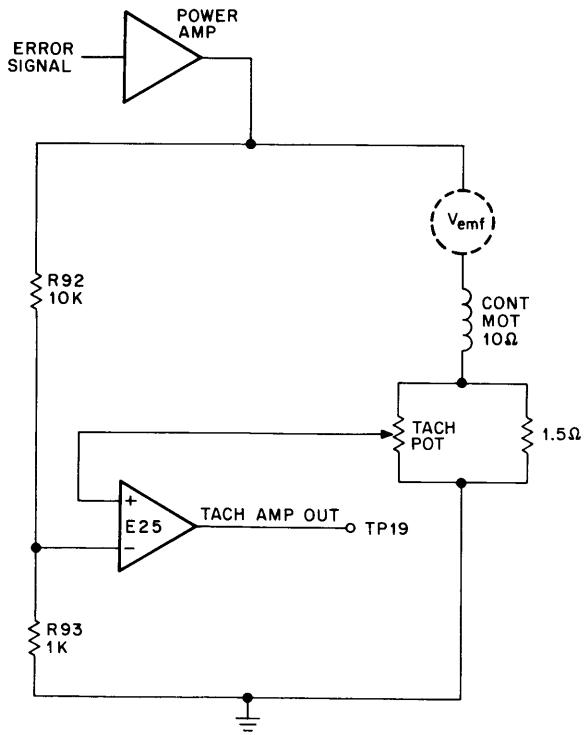

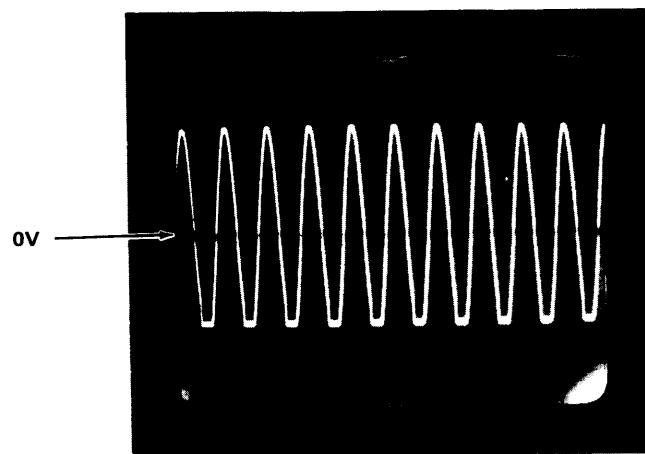

| 4.6.1.2 Tachometer Circuit . . . . .                      | 4-24 |

| 4.6.1.3 Error and Power Amplifiers . . . . .              | 4-26 |

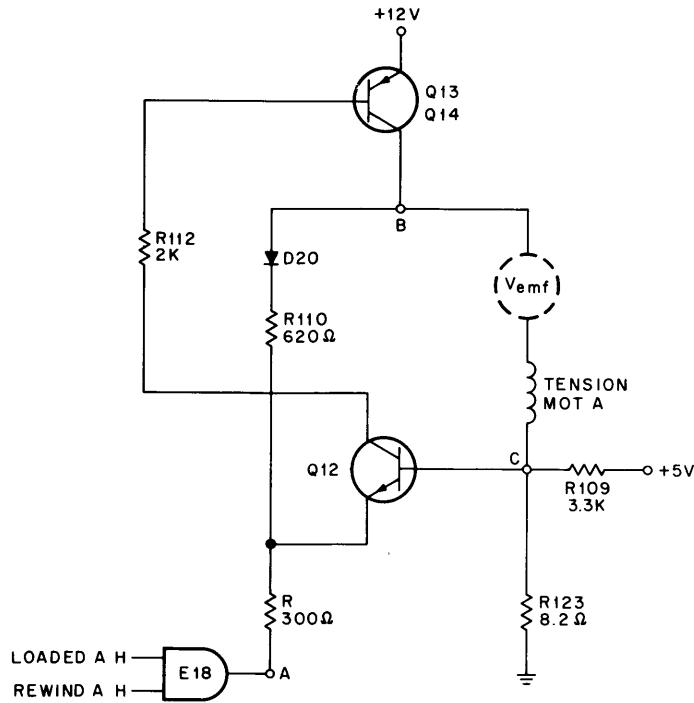

| 4.6.2 Tension Motor Control Circuit . . . . .             | 4-26 |

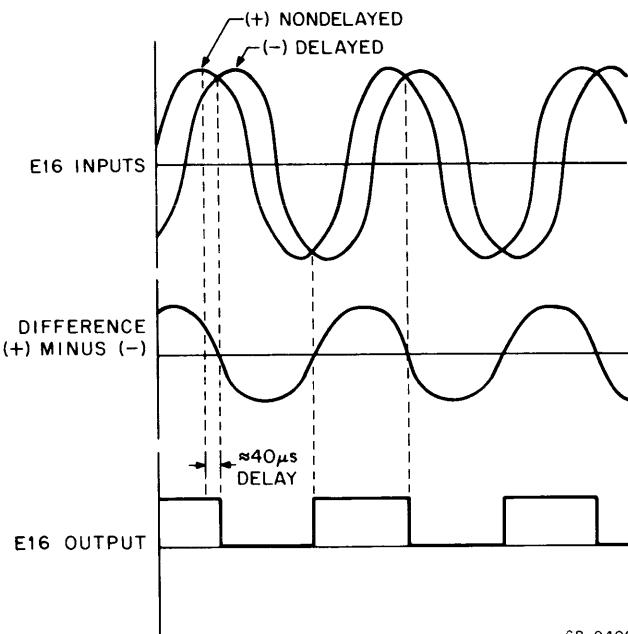

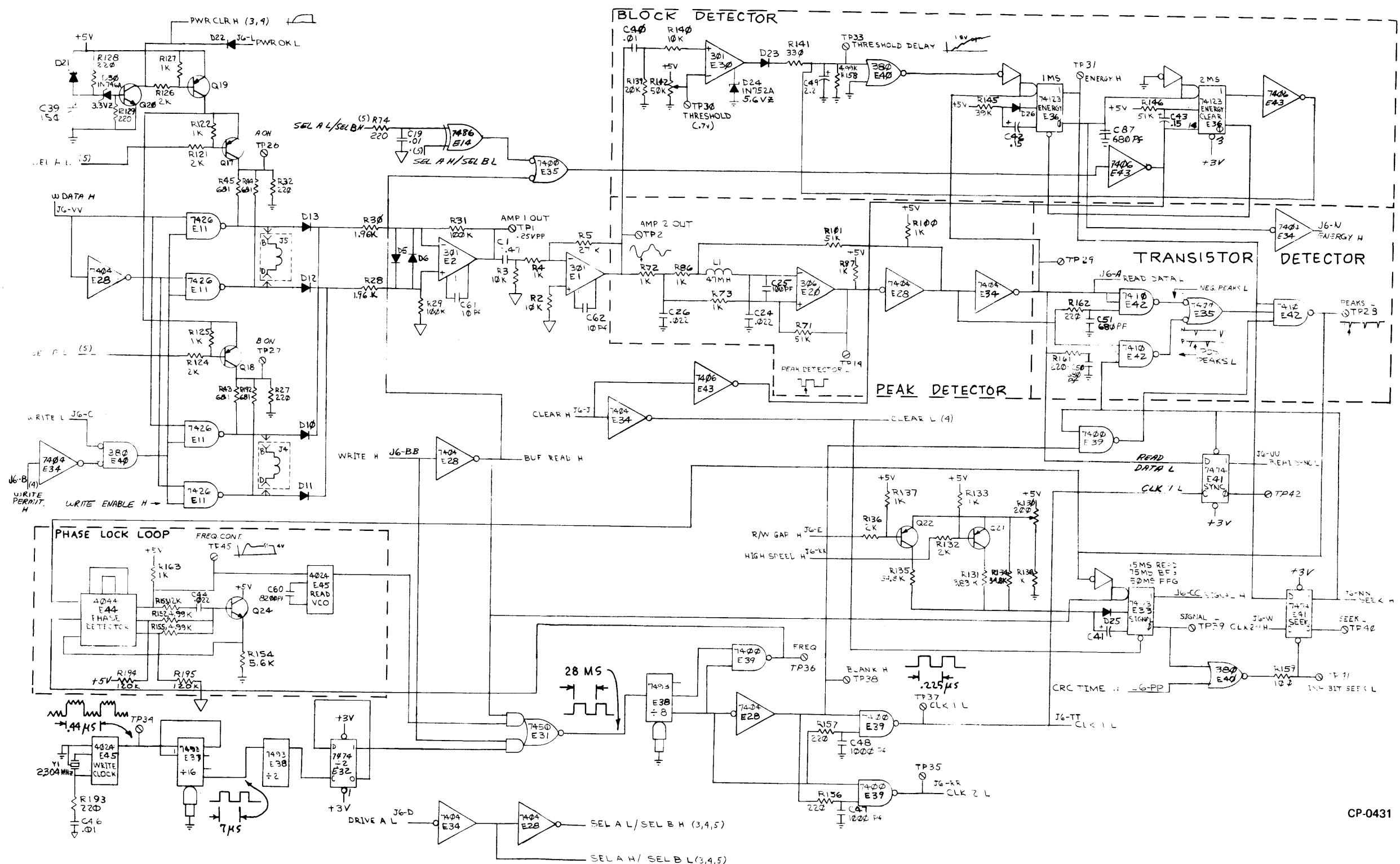

| 4.6.3 Phase Lock Loop . . . . .                           | 4-27 |

| 4.6.4 Peak Detector . . . . .                             | 4-28 |

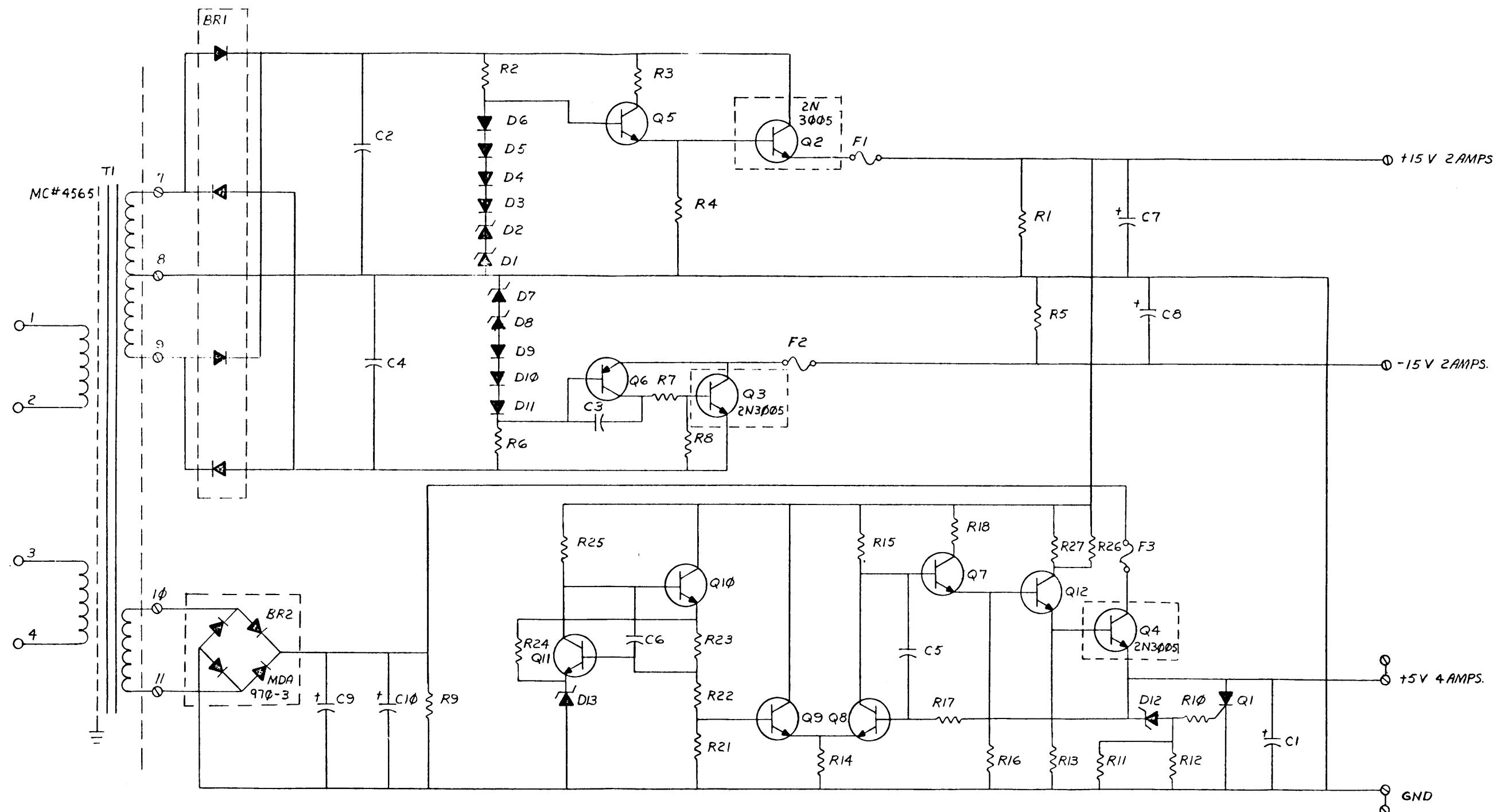

| 4.7 POWER SUPPLY . . . . .                                | 4-28 |

| 4.7.1 +15 and -15 Vdc Supply Operation . . . . .          | 4-29 |

| 4.7.2 +5 Vdc Supply Operation . . . . .                   | 4-29 |

| 4.7.3 Power Clear Circuit . . . . .                       | 4-30 |

| <br><b>CHAPTER 5 MAINTENANCE</b>                          |      |

| 5.1 RECOMMENDED TOOLS AND TEST EQUIPMENT . . . . .        | 5-1  |

| 5.2 PREVENTIVE MAINTENANCE . . . . .                      | 5-1  |

| 5.2.1 Quarterly PM (250 hours) . . . . .                  | 5-4  |

| 5.2.2 Semi-Annual PM (500 hours) . . . . .                | 5-4  |

| 5.2.3 Annual PM (1000 hours) . . . . .                    | 5-4  |

| 5.2.4 Biennial PM (2000 hours) . . . . .                  | 5-5  |

| 5.3 ADJUSTMENT PROCEDURES . . . . .                       | 5-6  |

| 5.3.1 Supply Voltages . . . . .                           | 5-7  |

| 5.3.2 Coarse Tachometer Adjustment . . . . .              | 5-7  |

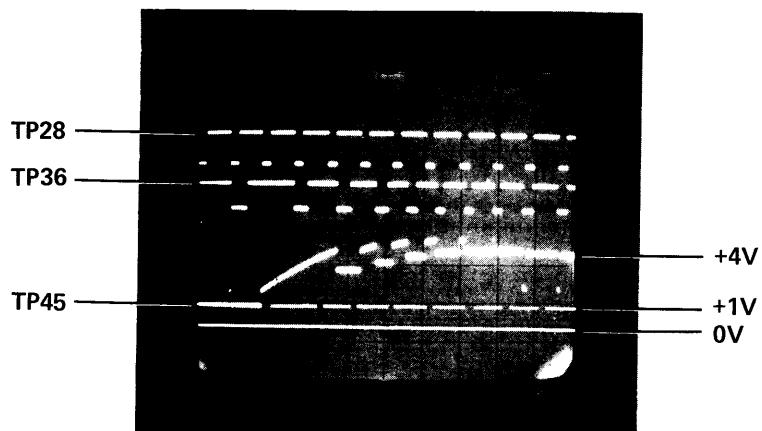

| 5.3.3 Servo Loop . . . . .                                | 5-9  |

| 5.3.3.1 Coarse Speed . . . . .                            | 5-9  |

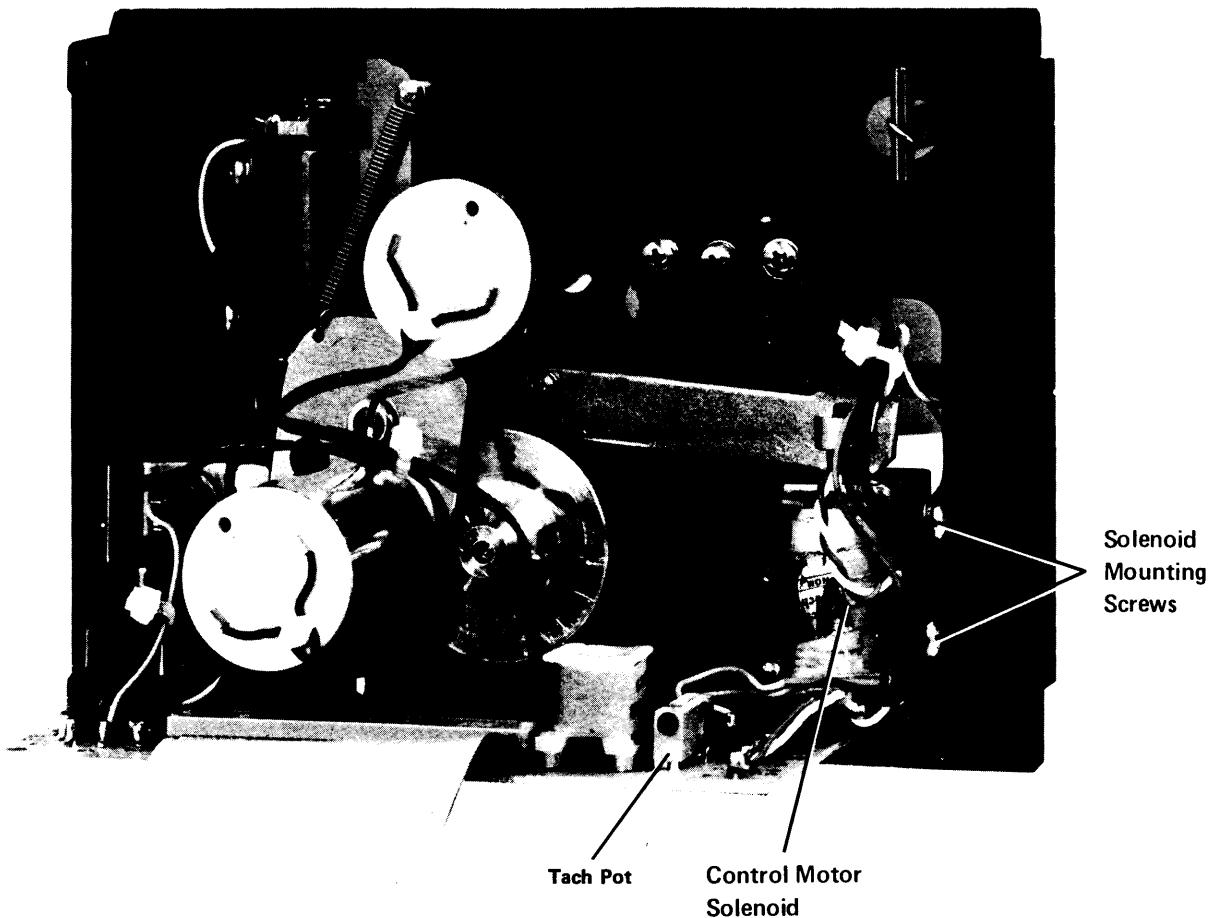

| 5.3.3.2 Control Motor Solenoid . . . . .                  | 5-10 |

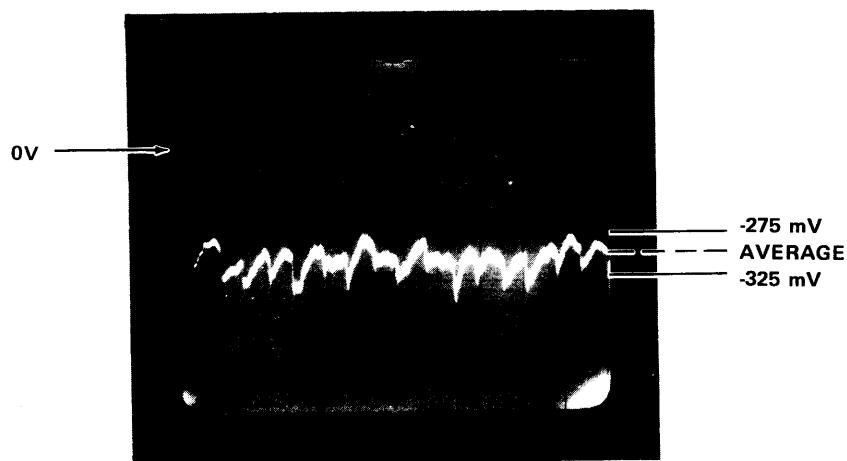

| 5.3.3.3 Balance . . . . .                                 | 5-11 |

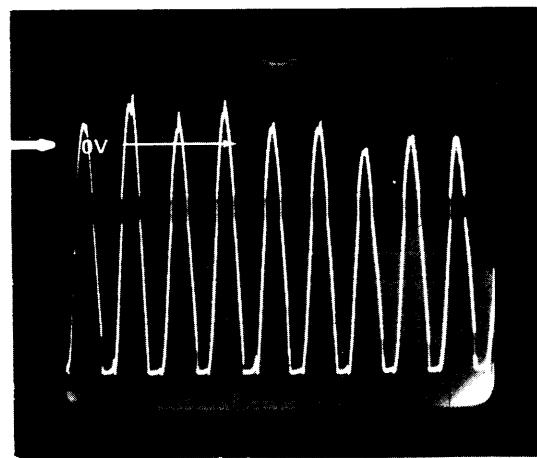

| 5.3.3.4 Fine Tachometer Adjustment . . . . .              | 5-13 |

| 5.3.3.5 Fine Speed . . . . .                              | 5-13 |

| 5.3.4 Head Skew . . . . .                                 | 5-14 |

| 5.3.5 -12 Vdc Regulator (Deceleration Ramp) . . . . .     | 5-16 |

| 5.3.6 Write File Gap One-Shot . . . . .                   | 5-17 |

| 5.3.7 Gap Time One-Shot . . . . .                         | 5-17 |

| 5.3.8 Threshold . . . . .                                 | 5-18 |

| 5.3.9 Signal One-Shot . . . . .                           | 5-19 |

| 5.3.10 Tape Blank One-Shot . . . . .                      | 5-20 |

| 5.4 TEST PROGRAMS AND DIAGNOSTIC ROUTINES . . . . .       | 5-21 |

| 5.4.1 PDP-8 Tape Motion Routines . . . . .                | 5-21 |

| 5.4.2 PDP-8 Diagnostic Routine . . . . .                  | 5-22 |

| 5.4.3 PDP-11 Tape Motion Routines . . . . .               | 5-22 |

| 5.4.4 PDP-11 Diagnostics Routines . . . . .               | 5-23 |

| 5.5 CORRECTIVE MAINTENANCE . . . . .                      | 5-23 |

| 5.5.1 Troubleshooting . . . . .                           | 5-23 |

| 5.5.2 Power, DC . . . . .                                 | 5-24 |

| 5.5.3 Drive Status (Figure A-6) . . . . .                 | 5-24 |

| 5.5.4 Drive Servo Balance . . . . .                       | 5-25 |

| 5.5.5 Drive Speed (R/W and Search) (Figure A-5) . . . . . | 5-25 |

| 5.5.6 Servo Ramp (Figure A-5) . . . . .                   | 5-26 |

| 5.5.7 Tension Motor Circuits (Figure A-5) . . . . .       | 5-26 |

## CONTENTS (Cont)

|        |                                                         | Page |

|--------|---------------------------------------------------------|------|

| 5.5.8  | Write Clock (Figure A-7) . . . . .                      | 5-27 |

| 5.5.9  | Signal One-Shot (Figure A-7) . . . . .                  | 5-27 |

| 5.5.10 | Preliminary Data Handling (Figure A-7) . . . . .        | 5-28 |

| 5.5.11 | Phase-Lock-Loop and Reading Data (Figure A-7) . . . . . | 5-28 |

## APPENDIX A REFERENCE DRAWINGS

### ILLUSTRATIONS

| Figure No. | Title                                              | Page |

|------------|----------------------------------------------------|------|

| 1-1        | Capacity and Data Rate vs Block Length . . . . .   | 1-4  |

| 1-2        | Location of Major Assemblies and Systems . . . . . | 1-6  |

| 1-3        | Cassette Tape Drive . . . . .                      | 1-7  |

| 1-4        | Cassette Loaded . . . . .                          | 1-9  |

| 2-1        | Transport Unpacking . . . . .                      | 2-2  |

| 2-2        | Cassette Loading Sequence . . . . .                | 2-4  |

| 4-1        | Typical Tape Format . . . . .                      | 4-1  |

| 4-2        | Rewind Flow Chart . . . . .                        | 4-3  |

| 4-3        | Back Block/File Gap Flow Chart . . . . .           | 4-4  |

| 4-4        | Write Data Block . . . . .                         | 4-6  |

| 4-5        | Illegal Command Sequence . . . . .                 | 4-8  |

| 4-6        | Command Topology . . . . .                         | 4-9  |

| 4-7        | Typical Phase Encoded Waveform . . . . .           | 4-15 |

| 4-8        | Write Timing . . . . .                             | 4-17 |

| 4-9        | Simplified Blank H and Read Clock Timing . . . . . | 4-20 |

| 4-10       | Read Timing . . . . .                              | 4-21 |

| 4-11       | Simplified Control Motor Servo System . . . . .    | 4-23 |

| 4-12       | Tachometer Circuit . . . . .                       | 4-25 |

| 4-13       | Rewind Control Circuit . . . . .                   | 4-27 |

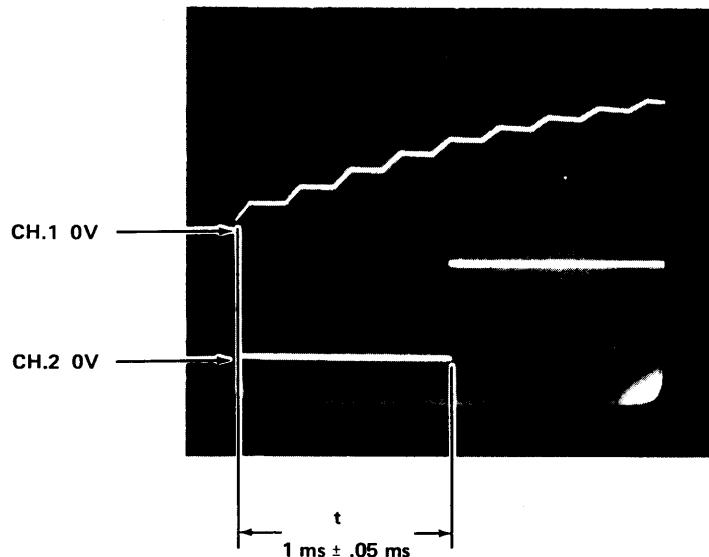

| 5-1        | Coarse Tachometer Adjustments . . . . .            | 5-8  |

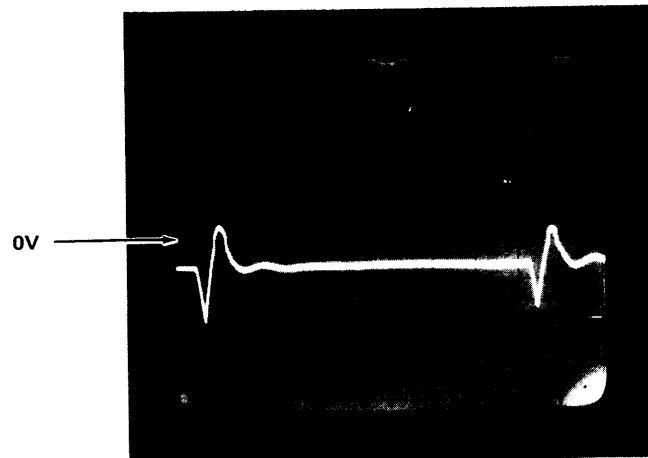

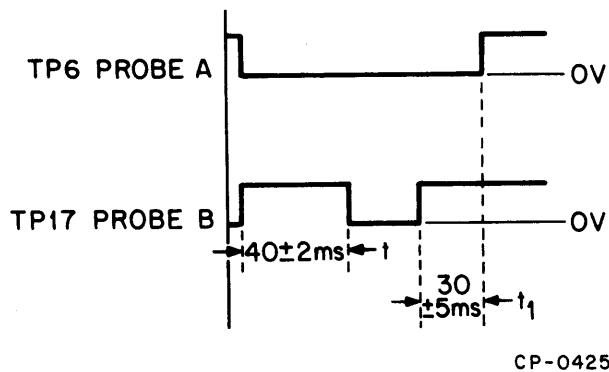

| 5-2        | Control Motor Solenoid Adjustment . . . . .        | 5-10 |

| 5-3        | Solenoid Mounting Screws . . . . .                 | 5-11 |

| 5-4        | Fine Tachometer Adjustments . . . . .              | 5-12 |

| 5-5        | Fine Speed Adjustment . . . . .                    | 5-14 |

| 5-6        | (Skew) Adjustment . . . . .                        | 5-15 |

| 5-7        | Head Skew Adjustment . . . . .                     | 5-15 |

| 5-8        | -12 Vdc Regulator Adjustment . . . . .             | 5-16 |

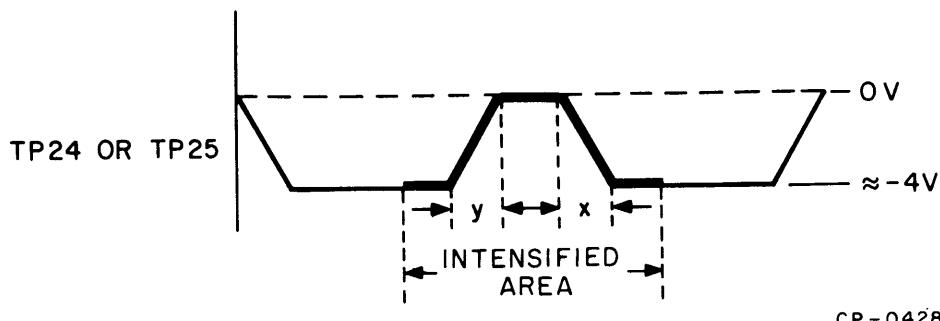

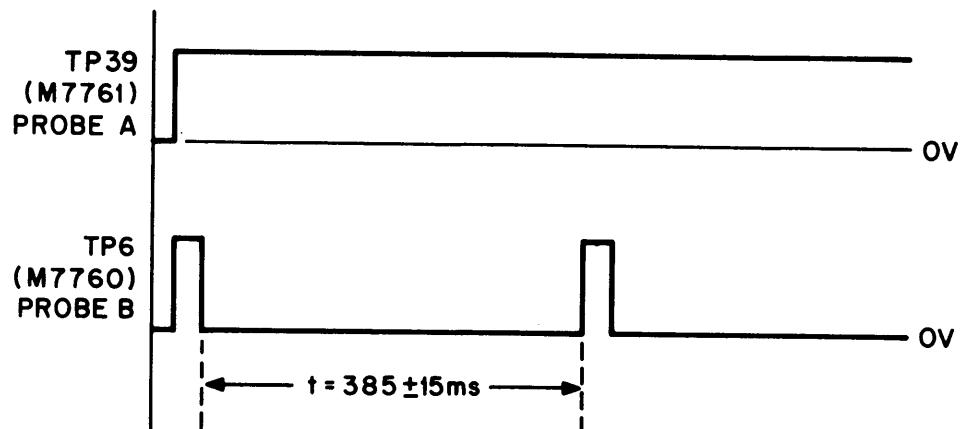

| 5-9        | Write File Gap Waveform . . . . .                  | 5-17 |

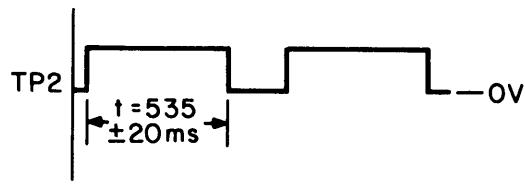

| 5-10       | Gap Time Waveform . . . . .                        | 5-18 |

| 5-11       | Threshold Waveform . . . . .                       | 5-19 |

| 5-12       | Signal Time Waveform . . . . .                     | 5-20 |

| 5-13       | Tape Blank Waveform . . . . .                      | 5-21 |

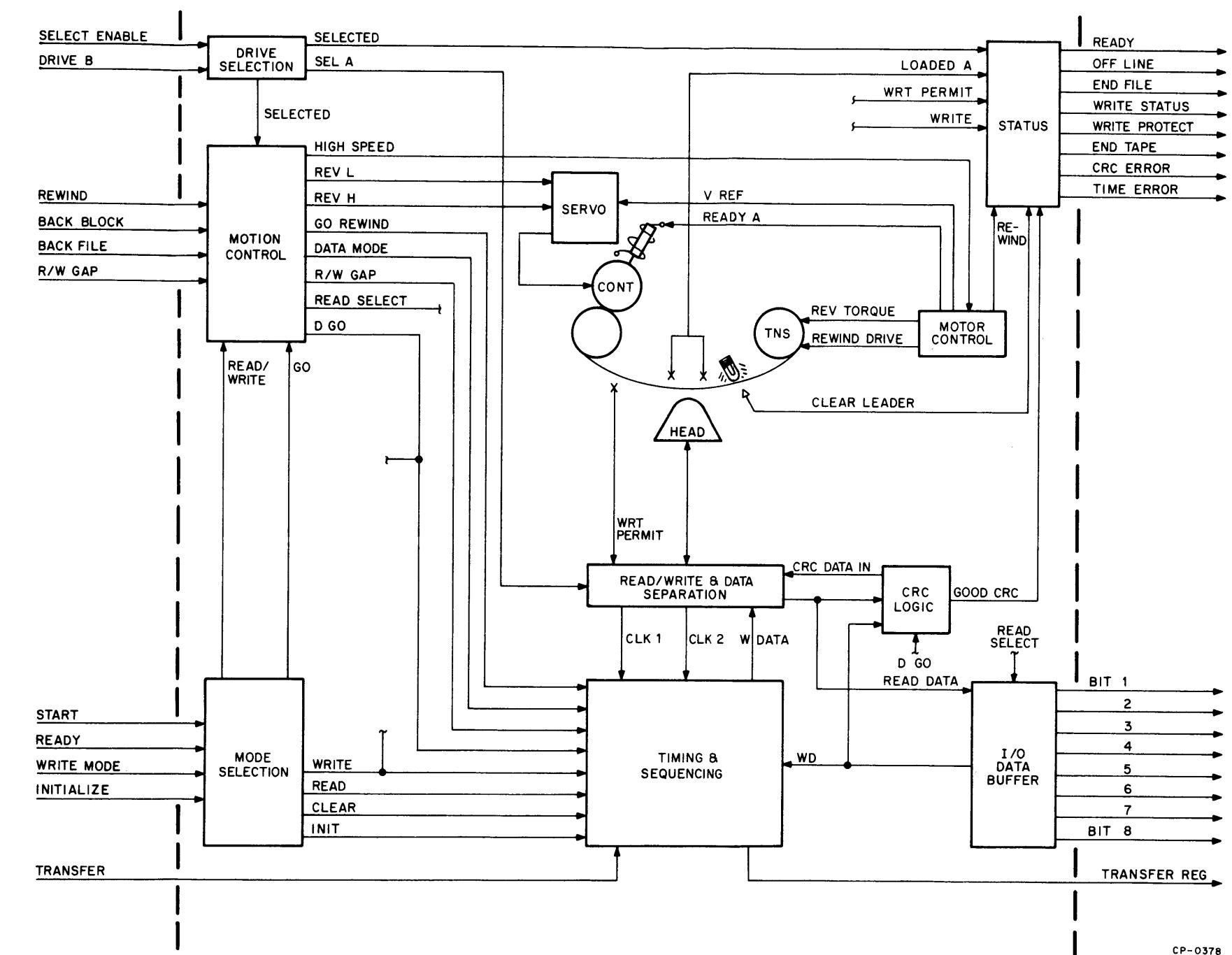

| A-1        | Functional Block Diagram . . . . .                 | A-3  |

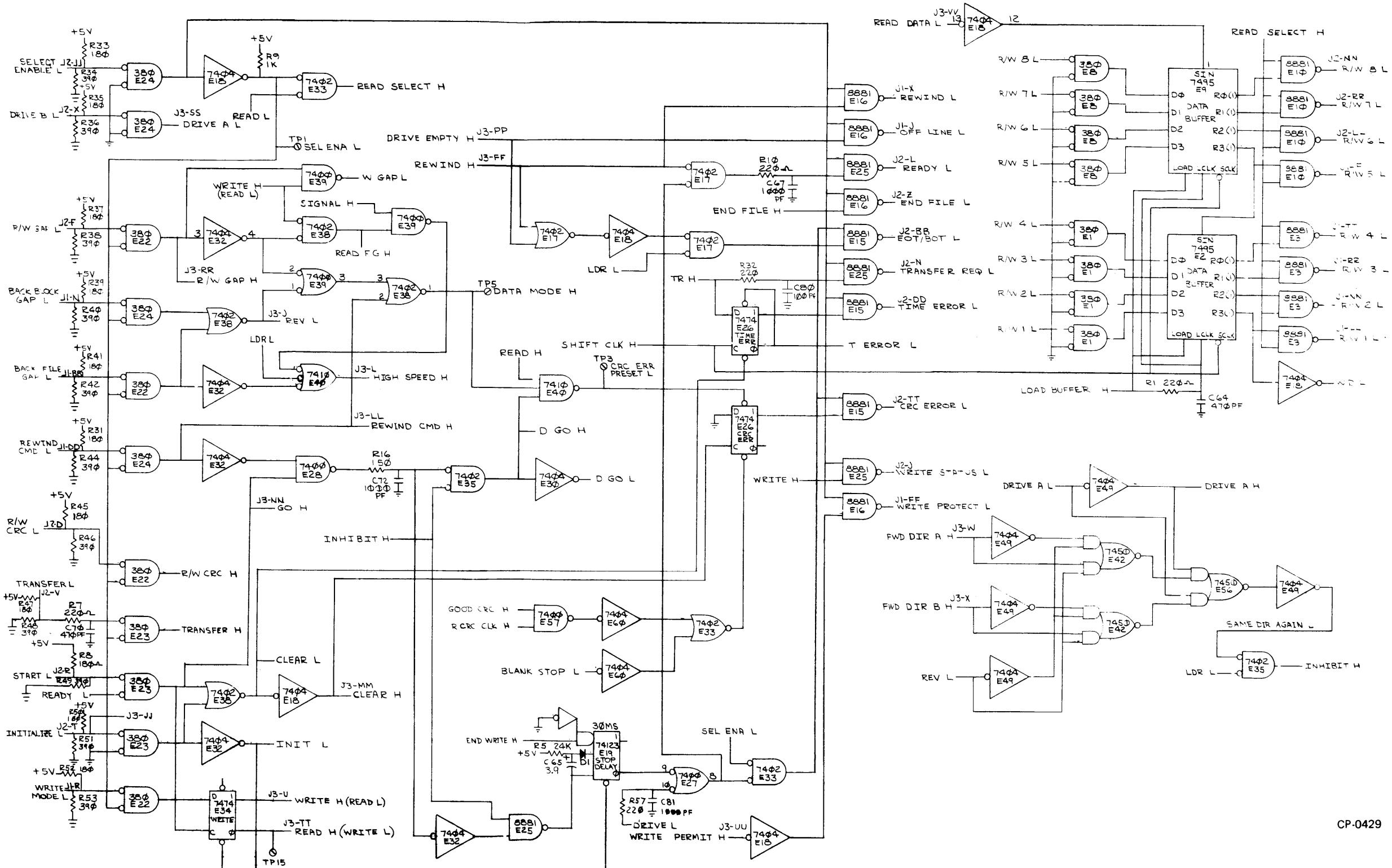

| A-2        | Interface Logic . . . . .                          | A-5  |

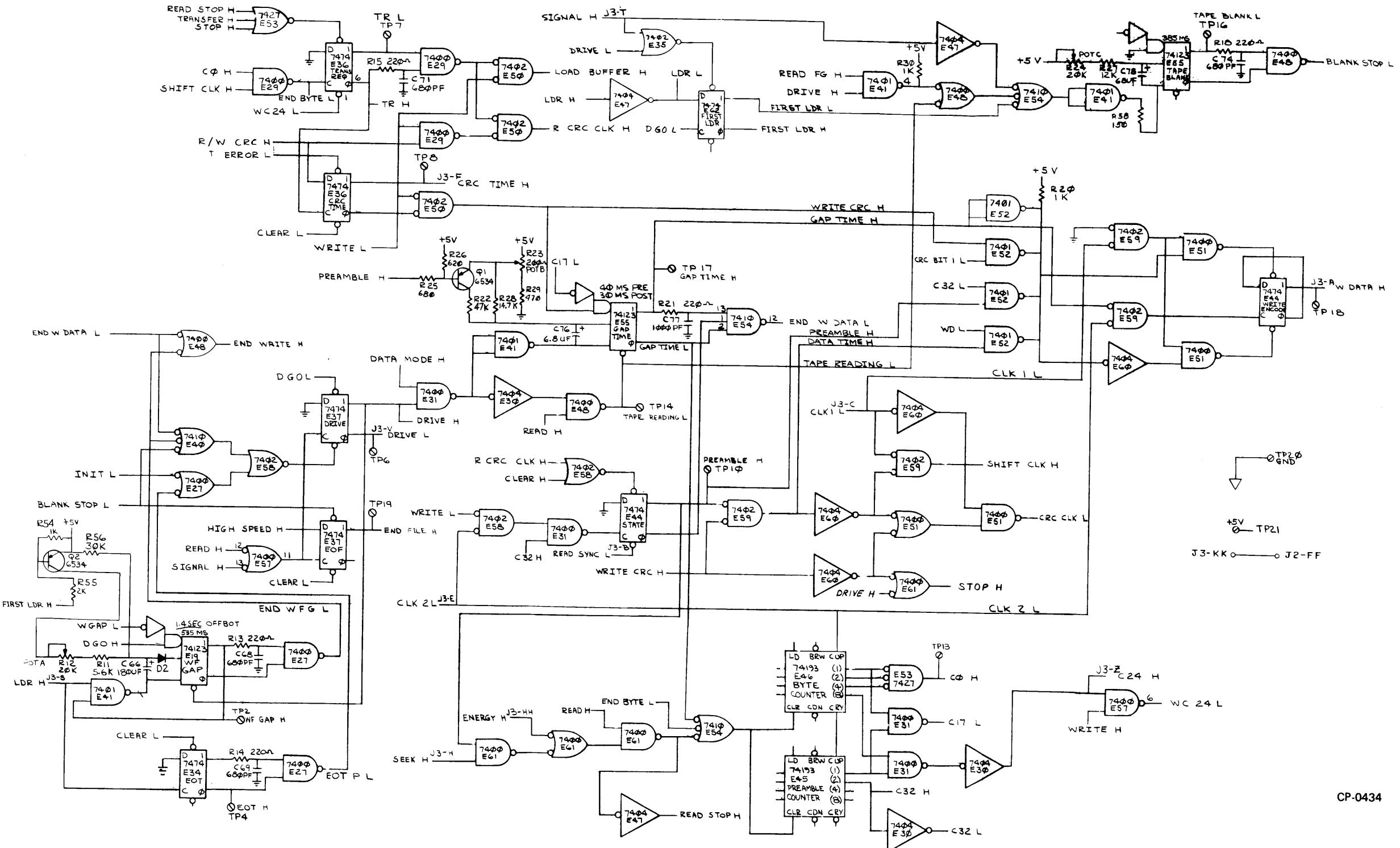

| A-3        | Formatter Logic . . . . .                          | A-7  |

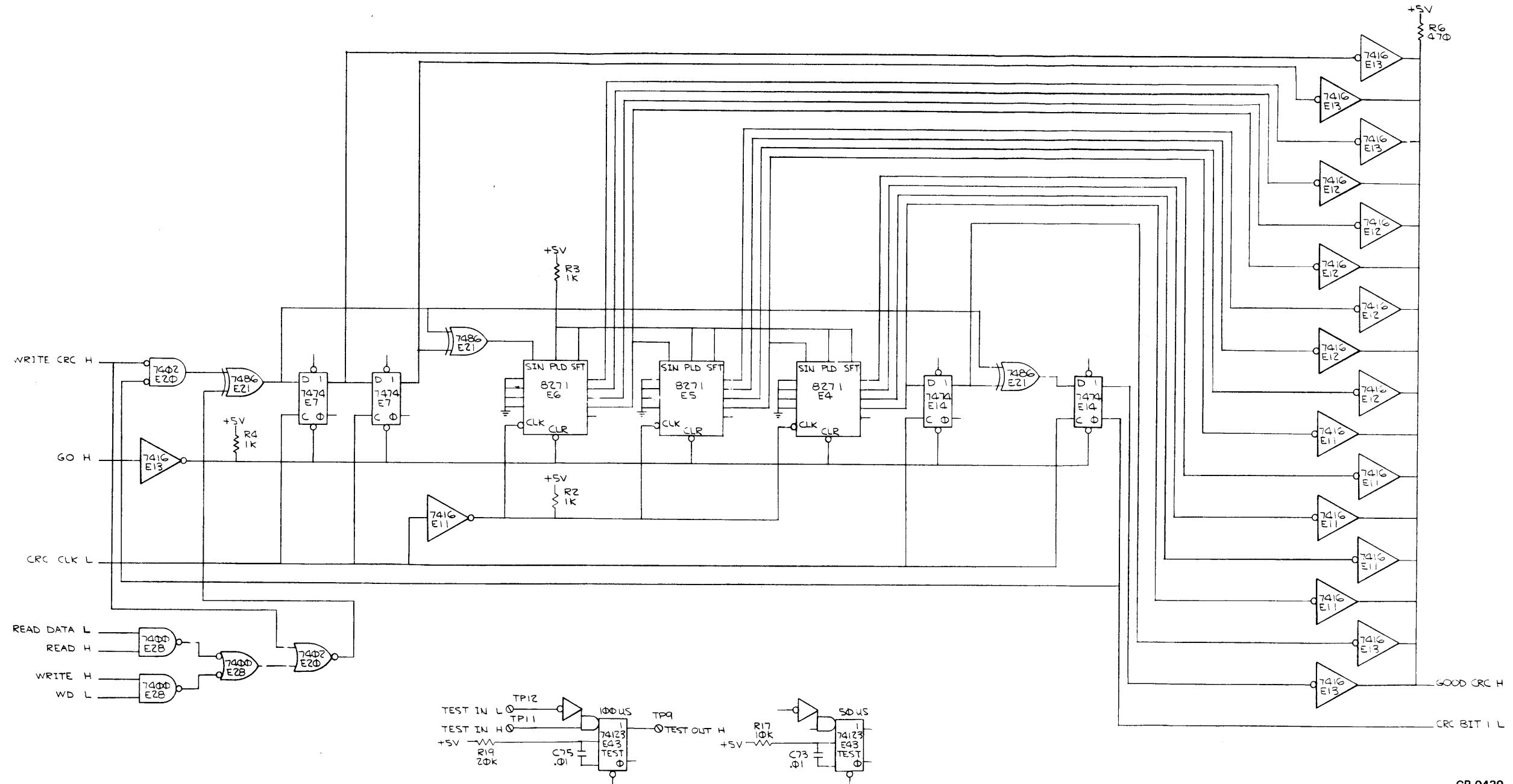

| A-4        | CRC Logic . . . . .                                | A-9  |

| A-5        | Motor and Servo Logic . . . . .                    | A-11 |

| A-6        | Rewind Logic . . . . .                             | A-13 |

| A-7        | Read/Write Logic . . . . .                         | A-15 |

| A-8        | H751 Power Supply . . . . .                        | A-17 |

## TABLES

| Table No. | Title                                          | Page |

|-----------|------------------------------------------------|------|

| 1-1       | Performance Specifications . . . . .           | 1-2  |

| 5-1       | Recommended Tools and Test Equipment . . . . . | 5-2  |

| 5-2       | Preventive Maintenance Schedule . . . . .      | 5-3  |

| 5-3       | Voltage Check . . . . .                        | 5-7  |

| 5-4       | Servo Loop Adjustments: Summary . . . . .      | 5-9  |

TU60 DECassette Tape Transport

# CHAPTER 1

## GENERAL INFORMATION

### 1.1 INTRODUCTION

The TU60 DECassette Tape Transport is a solid state, magnetic tape, data storage device. This device is composed of two individual tape drives and two electronic modules that contain all the logic and circuit components necessary for data formatting, error checking, and cassette housekeeping. The associated processor contains an interface module which is capable of: converting the processor codes into commands for transmission to the TU60, interpreting status flags received from the TU60, and storing input/output data. Each interface module can control one TU60 (2 drives). An internal H751 Power Supply furnishes +5 Vdc logic power and +15 & -15 Vdc operating power for the drive motors and operational amplifiers.

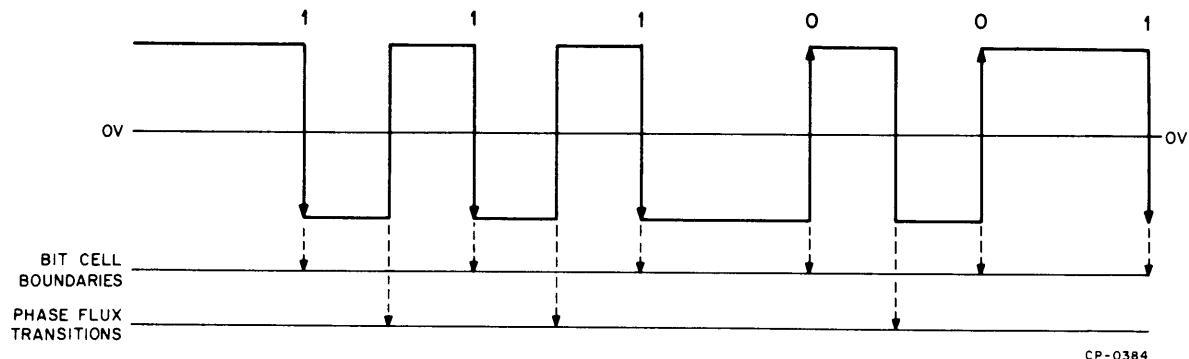

During a write operation, 8-bit data bytes are parallel transferred from the interface to the TU60, phase encoded, and serially recorded on the tape. Except for the tape length, there is no maximum limit to the number of bytes that may be grouped into a data block; however, it is not possible to replace an individual block on a recorded tape.

During a read operation, the self clocking data bits are serially read from the tape, then parallel transferred to the interface at a peak transfer rate of 562 bytes per second.

Tape motion within the digital cassette is directly controlled by two dc motors, without the use of capstans or pinch rollers. Because of this direct reel-to-reel drive system, tape speed across the read/write head varies as the take-up reel fills with tape. The tape speed for a read/write operation is approximately 6 inches per second at the beginning of the tape; however, the speed increases to approximately 12 inches per second at the end of the tape. Thus, the data blocks are written with varying bit densities, but at a constant frequency along the tape. The motion control logic within the transport ensures that tape motion stops only at a block or file gap.

### 1.2 CASSETTE RESTRICTIONS

It is extremely important that only DEC, 100 percent certified, Digital Tape Cassettes be used on the TU60 tape drives. The "heavy base" tape within the Digital Equipment Corporation Cassettes was specifically chosen to be compatible with the high drive tensions of the TU60. In addition, the head pressure pad material of the cassette has been carefully selected to allow proper tape stacking. For optimal operational characteristics, the dynamics of each tape drive require the use of only Digital Equipment Corporation Cassettes.

**DO NOT ATTEMPT TO USE AN AUDIO CASSETTE ON THE TU60 TAPE DRIVES.** Since the tape within an audio cassette is not designed to tolerate the high drive tensions of the TU60, use of this type cassette will result in extremely rapid deterioration of the tape and subsequent failure of the drive due to excessive tape oxide deposits on the read/write head and tape guides.

Because the DEC cassette is relatively more expensive than an audio cassette, it should not be used in place of an audio cassette. The lower "high-frequency rolloff" of the digital tape makes the DEC cassette a poor substitute for audio operations. In addition, the coefficient of friction of the DEC tape does not allow tape motion by capstan and pinch rollers as is usually the case with most audio recorders.

In short, the TU60 DECassette Tape Transport and the DEC, 100 percent certified, Digital Cassette are designed to be used together. Use of any cassette other than the DEC cassette may void the transport warranty.

### 1.3 SPECIFICATIONS

Table 1-1 lists the performance specifications of the TU60 DECassette Tape Transport. To obtain the specified data reliability, use only DEC, 100 percent certified, Digital Tape Cassettes. DEC cassettes are especially constructed to be compatible with the TU60 tape drive dynamics. Use of any other cassette will increase the data error rate and decrease the tape and transport longevity.

**Table 1-1**

Performance Specifications

| Characteristic                 | Parameter                                                                              |

|--------------------------------|----------------------------------------------------------------------------------------|

| <b>Model Designations</b>      |                                                                                        |

| TU60 AA                        | 115 Vac, rack mounted                                                                  |

| TU60 AB                        | 230 Vac, rack mounted                                                                  |

| <b>Electrical Requirements</b> |                                                                                        |

| Input Voltage                  | 95 to 130 Vac @ 47-63 Hz<br>190 to 260 Vac @ 47-63 Hz                                  |

| Input Current                  | 1.0A                                                                                   |

| Power Dissipation              | 120W (409.8 Btu/hr or 103.4 Kcal/hr) max                                               |

| Circuit Breaker Ratings        | 7A @ 115 Vac (resettable)<br>4A @ 230 Vac (resettable)                                 |

| Power Supply                   | See Paragraph 4.7 for specifications                                                   |

| <b>Interface Signals</b>       |                                                                                        |

| Logic Levels*                  | True = 0V<br>False = +3V                                                               |

| Loads (TTL compatible)         | Inputs: 180Ω to +5 Vdc, 390Ω to gnd<br>Outputs: Open collector, 30 mA max sink current |

| <b>Environment</b>             |                                                                                        |

| Operating Temperature          | 50 to 105°F (10 to 40°C)                                                               |

\*Except PWR OK L, Logic True = 0.9V

Logic False = open

Max Sink Current = 2 mA

**Table 1-1 (Cont)**

**Performance Specifications**

| Characteristic                    | Parameter                                                                                           |

|-----------------------------------|-----------------------------------------------------------------------------------------------------|

| <b>Environment (Cont)</b>         |                                                                                                     |

| Cassette Storage Temperature      | 40 to 122°F (5 to 50°C)                                                                             |

| Operating Relative Humidity       | 20 to 80% (no condensation)                                                                         |

| Altitude                          | 0 to 10,000 ft (0 to 3048m)                                                                         |

| <b>Storage Medium</b>             |                                                                                                     |

| Type                              | DEC, 100% certified, Digital Tape Cassettes                                                         |

| Tape Width                        | 0.150 in. (0.381 cm)                                                                                |

| Tape Thickness                    | 1 mil, 0.30 mil oxide                                                                               |

| Tape Life                         | Guaranteed at least 1000 end-to-end forward passes<br>Typically 2000–6000 end-to-end forward passes |

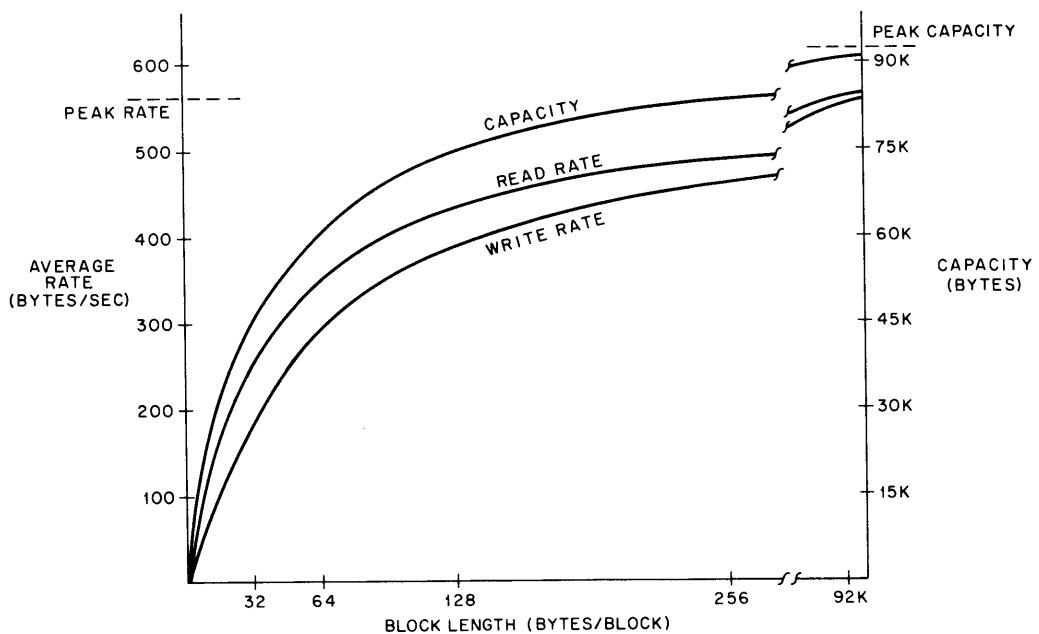

| Capacity                          | ≥93K bytes, average rate: see Figure 1-1                                                            |

| Recording Density                 | 350 to 700 bits/in. (889 to 1778 bits/cm)                                                           |

| Recording Method                  | Phase Encoding                                                                                      |

| Format                            | Variable block length (hardware formatted)                                                          |

| Drive Method                      | Direct (reel-to-reel)                                                                               |

| <b>Average Operational Speeds</b> |                                                                                                     |

| Read/Write                        | 9.6 in./sec (3.78 cm/sec)                                                                           |

| Search                            | 22 in./sec (8.66 cm/sec)                                                                            |

| Rewind                            | 100 to 150 in./sec (39.37 to 59.05 cm/sec)                                                          |

| Data Transfer Rate                | 562 bytes/sec, average rate: see Figure 1-1                                                         |

| <b>Tape Motion Times</b>          |                                                                                                     |

| Start/Stop                        | < 20 ms read/write; < 45 ms search (linear ramp controlled)                                         |

| Rewind                            | 30 sec (max), < 20 sec typical                                                                      |

Table 1-1 (Cont)

Performance Specifications

| Characteristic               | Parameter                                                            |

|------------------------------|----------------------------------------------------------------------|

| <b>Bit Error Rate</b>        |                                                                      |

| Write Errors                 | 1 in $10^8$                                                          |

| Read Errors                  | 1 in $10^8$ (unrecoverable)<br>1 in $10^7$ (recoverable - 3 rereads) |

| <b>Dimensions and Weight</b> |                                                                      |

| Width                        | 19 in. (0.48 m)                                                      |

| Depth                        | 18-1/4 in. (0.46 m)                                                  |

| Height                       | 5-1/4 in. (0.13 m)                                                   |

| Weight                       | 32 lb (14.06 kg)                                                     |

Figure 1-1 Capacity and Data Rate vs Block Length

CP-0377

## 1.4 MAJOR ASSEMBLIES

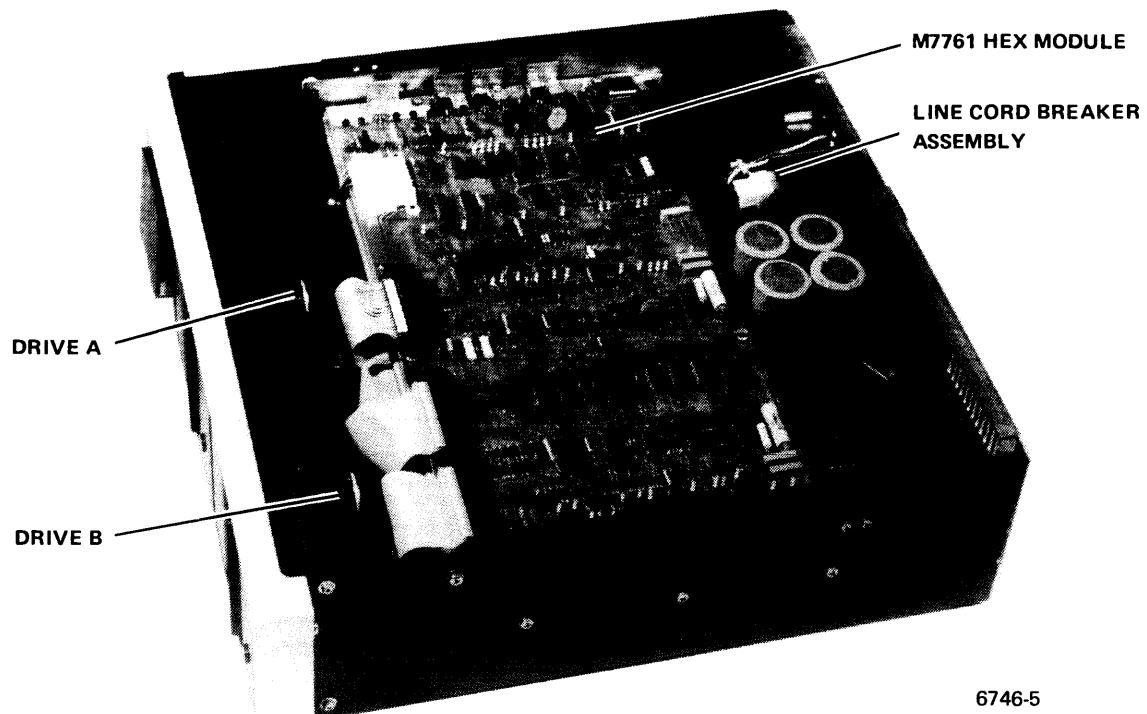

The TU60 Cassette Tape Transport is composed of the following major assemblies and systems:

- controls and indicators

- two tape drives

- two hex-sized (15.7 X 8.6 in. or 39.88 cm X 21.84 cm) logic modules

- a power supply (H751).

Figure 1-2 illustrates the locations and the subsequent paragraphs describe the functions of each of the major assemblies and systems.

### 1.4.1 Controls and Indicators

There are only three manual controls on the TU60. Each drive contains a separate REWIND pushbutton and a Power-On indicator. The Power ON/OFF toggle switch for the entire transport is located on the chassis rear panel. These manual controls and indicators perform the following functions:

- **REWIND** – Pressing this momentary contact pushbutton on one of the two drives, rewinds the tape on that drive, at high speed, to the Beginning-of-Tape (BOT) marker provided:

- a cassette is loaded

- tape is not moving under program control.

Pressing this switch during a program controlled operation has no effect.

- **Power ON/OFF** – Placing this switch in the ON position lights both Power-On indicators (located opposite the REWIND pushbuttons on the lower door of each drive) and activates the internal dc power supply. Conversely, placing this switch in the OFF position de-activates the power supply and turns off both Power-On indicators.

### 1.4.2 Drive Mechanism

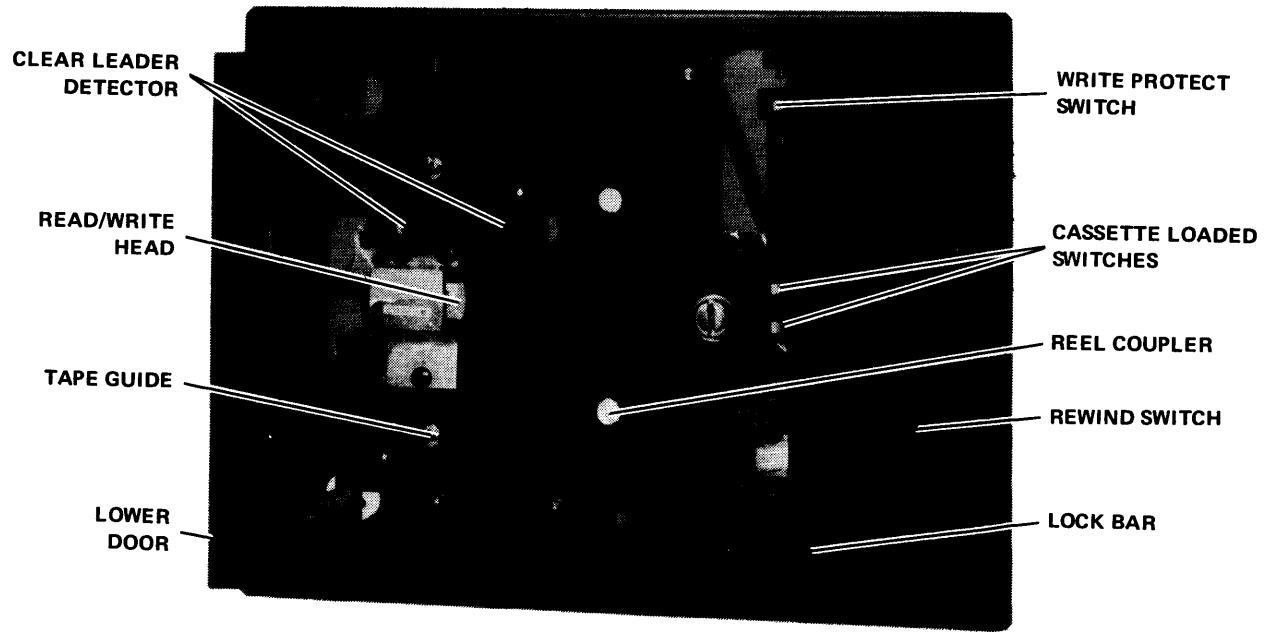

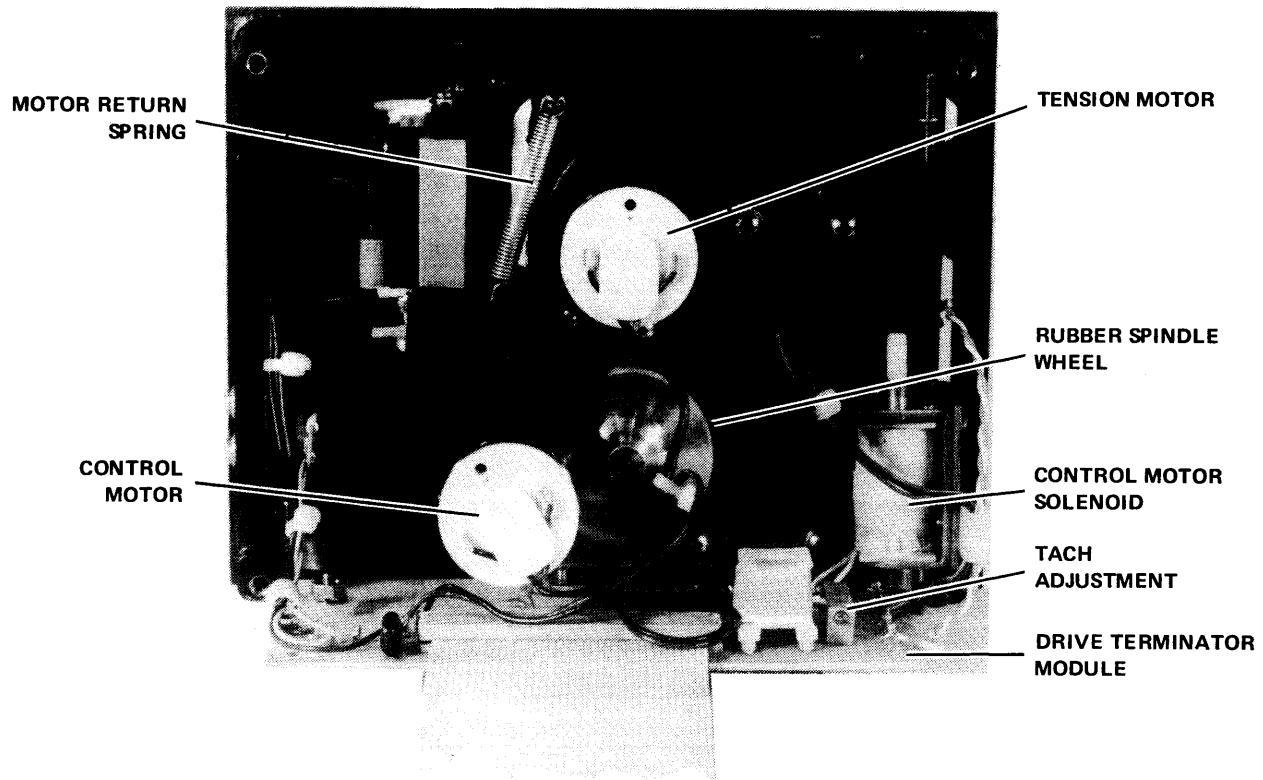

Each tape drive (Figure 1-3) consists of:

- a tension motor and a servo operated control motor

- a control motor solenoid

- various interlock microswitches

- a clear leader photodetector

- two tape guides and a read/write head.

(A) Logic Modules Down

(B) Logic Modules Up

6422-5

Figure 1-2 Location of Major Assemblies and Systems

6432-7

(A) Drive Front View

(B) Drive Rear View

6746-8

Figure 1-3 Cassette Tape Drive

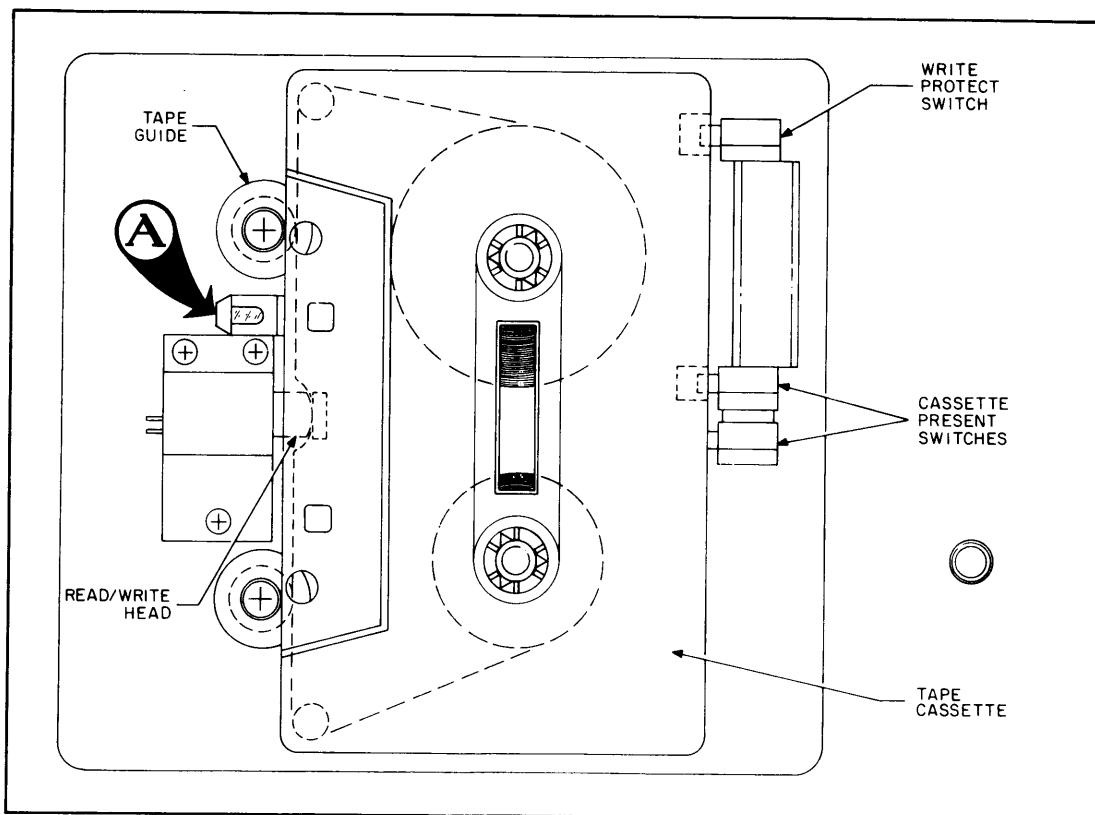

If the appropriate digital cassette is properly loaded, one of the cassette loaded microswitch actuators (located on the drive lock bar) extends into a recess on the cassette, while the other switch closes against the cassette case (Figure 1-4). This switch configuration removes the unloaded interlock condition and permits tape motion upon command. Similarly, if the write protect recess on the cassette case is opened (protect tab on cassette folded back), the write protect microswitch actuator extends into this recess and inhibits write operations. When commanded, tape motion from the supply reel, over the tape guides and read/write head, and onto the take-up reel is directly controlled by the tension and control motors.

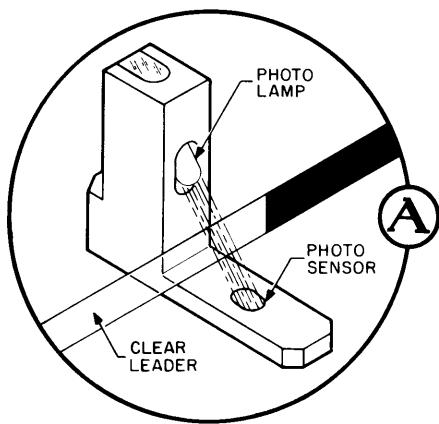

For a rewind operation (tape travel from lower to upper reel), the control motor solenoid is de-energized. This action allows the spring-loaded control motor to move away from the lower rubber sprocket wheel and thus permit the lower tape reel to turn freely. Simultaneously, the upper tension motor is turned on at constant speed to rewind the tape at rewind speed (100–150 ips) to the beginning-of-tape clear leader. Detection of the clear leader is accomplished by a photosensor (located in the drive baseplate) and a lamp which shines at an angle onto the photosensor. As tape passes between the lamp and the photosensor (Figure 1-4), light from the lamp is prevented, by the tape oxide, from reaching the photosensor. When the clear leader passes between these two elements, light from the lamp then shines through the clear leader and onto the photosensor, thus activating the sensor to stop tape motion.

For a read, write, or search operation, the control motor solenoid remains energized, holding the control motor against the rubber sprocket wheel. During these operations, a servo system governs the velocity of this motor, to control the tape motion. For forward motion, the control motor rotates counterclockwise, while a slight reverse torque is applied to the tension motor to maintain the proper tape tension. For reverse motion, the control motor rotates clockwise, while a greater torque is applied to the tension motor to take up the tape and thus maintain the proper tape tension.

#### **1.4.3 Logic**

The M7760 and M7761 hex-sized logic modules (Figure 1-2) within the TU60 are hinged mounted to the top of the transport chassis and swing upward for easy component access during maintenance. These hex modules are interconnected by a single jumper cable and they contain all the logic and circuit components necessary to perform data formatting, error checking (CRC generation and validation), bit to byte conversion, tape motion control, and cassette housekeeping. Since most of the controller functions are performed by the logic on these modules, the associated processor contains only an interface module which is capable of translating the processor codes into commands, interpreting status flags, and storing input/output data. Each tape drive has a flat cable which plugs into the upper hex module.

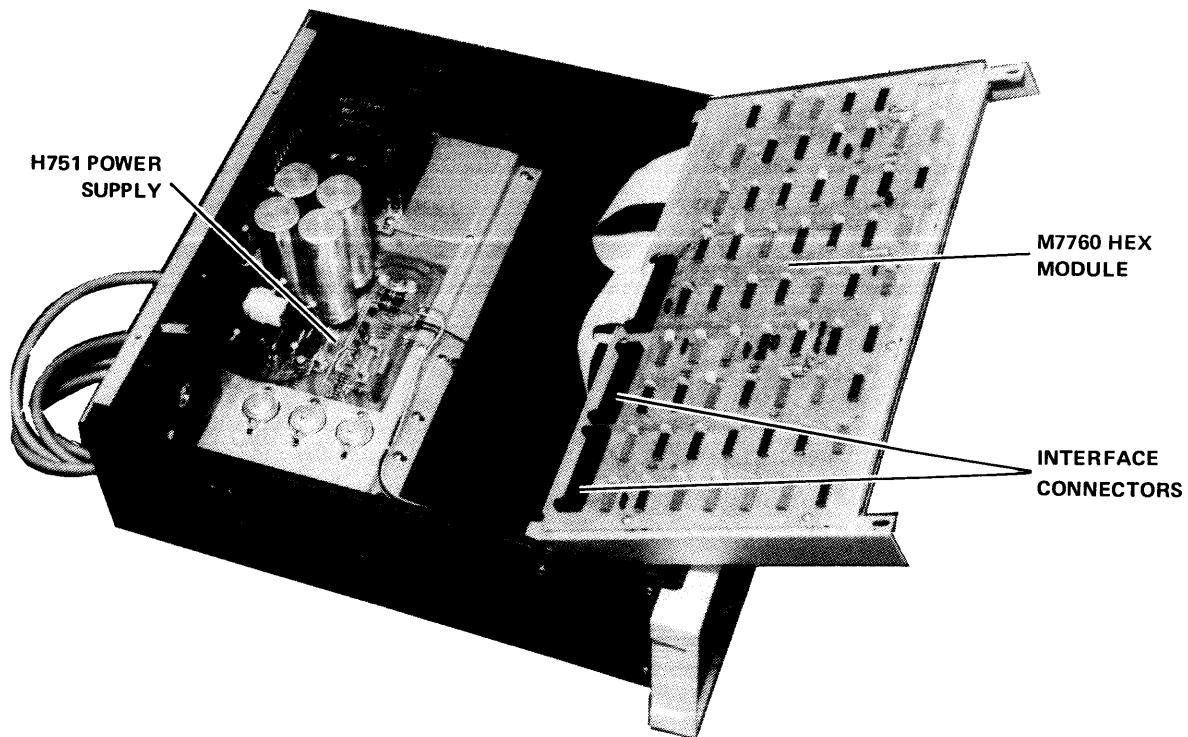

#### **1.4.4 H751 Power Supply**

The H751 Power Supply, located in the rear of the TU60 chassis, furnishes +15 and -15 Vdc to a precision 12V regulator on the M7761 module. The +12 and -12 Vdc regulator output is then supplied to the sprocket motors and operational amplifiers. In addition, the H751 Power Supply furnishes a +5 Vdc precision regulated output for the logic operation. By changing the line cord breaker assembly, this power supply can operate with either 115 or 230 Vac (50/60 Hz) input line voltage. Both internal supplies are fuse protected against overcurrent and the +5 Vdc supply has a crowbar overvoltage protection circuit. (Refer to Paragraph 4.5 for a detailed description of the power supply operation.)

CP-0391

Figure 1-4 Cassette Loaded

# CHAPTER 2

## INSTALLATION

### 2.1 UNPACKING AND INSPECTION

The TU60 DECassette Tape Transport can be shipped in a rack as an integral part of a system or in a separate container. If the transport is shipped in a rack, position the rack in the final installation location and unpack it as follows:

1. Open the rear door of the rack and remove the shipping bracket. Retain the bracket for possible return shipment.

2. Slide the transport out from the rack and remove the top cover.

3. Inspect the transport and report any damage to the carrier and to Digital Equipment Corporation.

If the transport is shipped in a separate container, use care while unpacking it. Do not drop or subject the transport to unreasonable impact. Unpack the transport as follows:

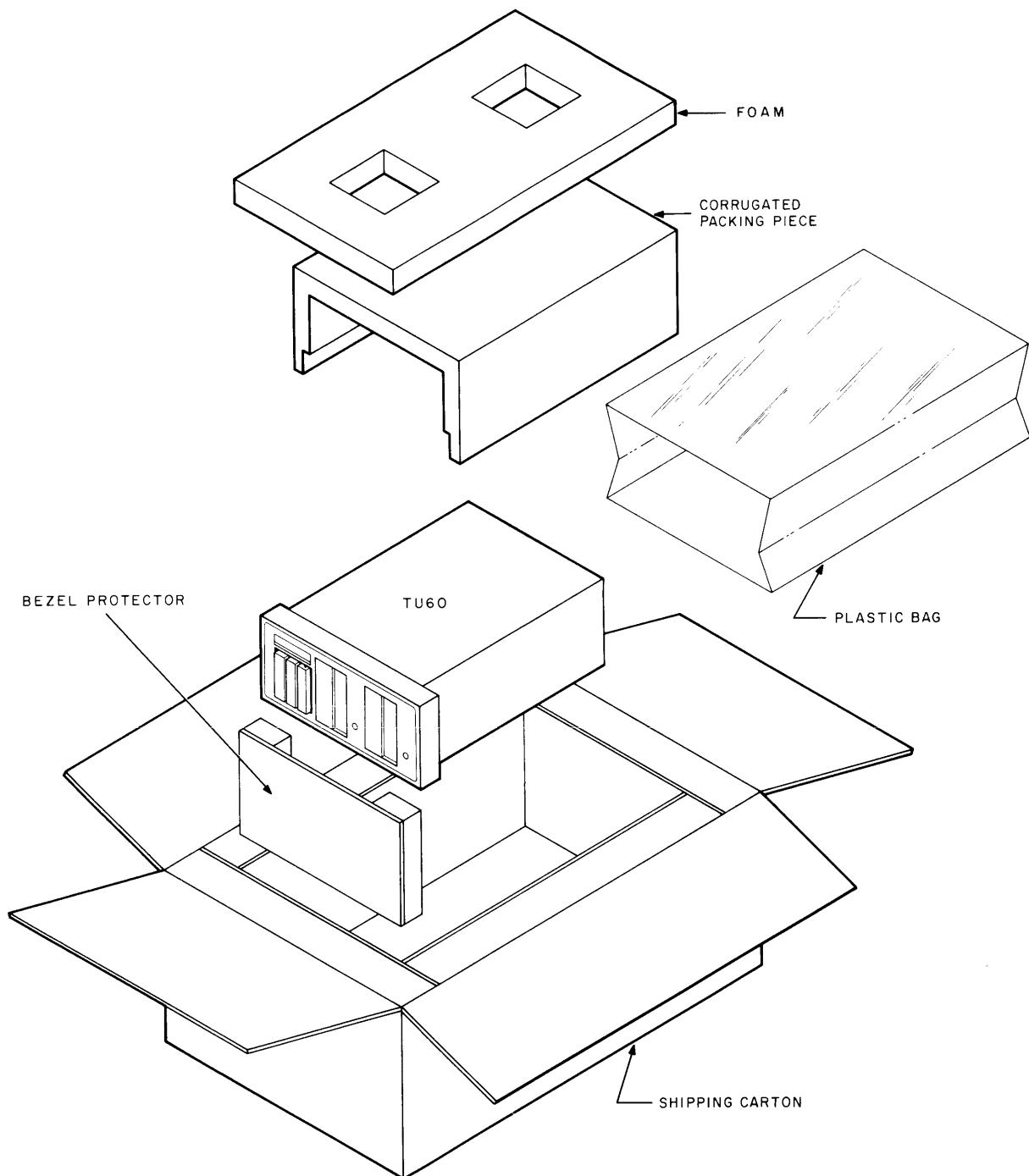

1. Open the carton (Figure 2-1) and remove the foam and corrugated packing pieces.

2. Lift the transport out of the carton and remove the plastic shipping bag.

3. Remove the transport top cover and retain all packing materials for possible return shipment.

4. Inspect the transport and report any damage to the carrier and to Digital Equipment Corporation.

### 2.2 ELECTRICAL INSTALLATION AND CHECKOUT

1. Check the power supply line cord breaker assembly to ensure that the transport is configured properly for the input power to be used. Line cord breaker assembly BC05H is for 115 Vac operation and BC05J is for 230 Vac operation.

2. Route the interface cables through the opening beneath the fan in the rear of the transport and connect them to J1 and J2 of the M7760 module in the TU60.

3. Route the opposite end of the interface cables through the cable strain reliefs and connect them to the interface. (Refer to the appropriate interface Power Wiring and Cable Diagram for the correct cable type and processor connection.)

CP-0394

Figure 2-1 Transport Unpacking

4. Plug the power cord into the switched ac line receptacle.

5. Place the Power ON/OFF switch (located on the chassis rear panel) in the ON position and ensure that the Power-On indicators light on both drives.

6. Load a test cassette (Paragraph 2.3.1) on each drive and momentarily press both REWIND pushbuttons. Ensure that the tape completely rewinds to the BOT clear leader (about 20 seconds).

7. Momentarily press both REWIND pushbuttons again and check that the drives rewind tape for about one second.

8. Run the appropriate diagnostic tests to ensure the proper electrical and mechanical operation.

## 2.3 OPERATION

### **IMPORTANT: READ THIS PARAGRAPH PRIOR TO DRIVE OPERATION.**

To obtain maximum performance and reliability from the TU60 Cassette Tape Transport, observe the following precautions and practices:

1. Before using a new cassette, or prior to using a cassette that has just been shipped or accidentally dropped;

- a. Load the cassette on a drive (Paragraph 2.3.1) and perform a rewind operation.

- b. Remove the cassette, turn it over, and perform another rewind operation.

This is done to pack the tape neatly in the cassette and also to place the full tape reel at the proper operating tension.

2. Do not expose the cassette to excessive heat or dust. Since most tape soft errors are caused by dust or dirt, it is imperative that the tape be kept clean.

3. When not in use, store the cassettes in the plastic storage boxes or other sealed containers.

4. Always rewind the tape to the BOT leader before removing the cassette from the drive.

### 2.3.1 Cassette Loading and Unloading

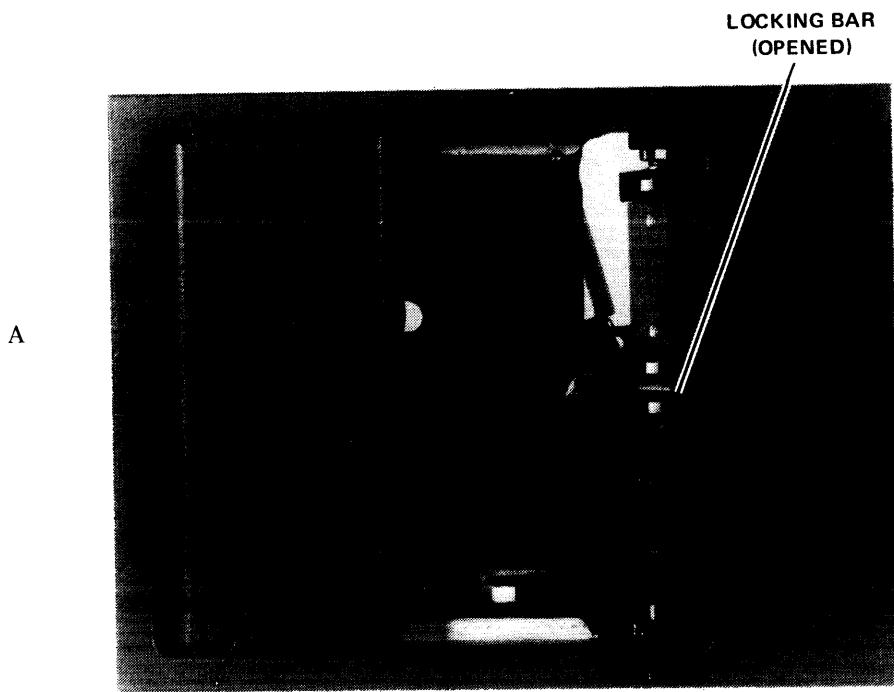

A cassette may be loaded on the drive with the drive locking bar either opened or closed; however, it is slightly easier to load a cassette with the bar opened. It is therefore recommended that the cassette be loaded as follows, with the locking bar opened (Figure 2-2A):

1. Configure the cassette write protect tab (Figure 2-2B) for the desired operation.

#### **NOTE**

The write protect tab is located on the cassette top right, when viewed with the label side up. To inhibit a write operation, fold this tab back to open the cassette recess. To allow a write operation, return the write protect tab to close the recess hole.

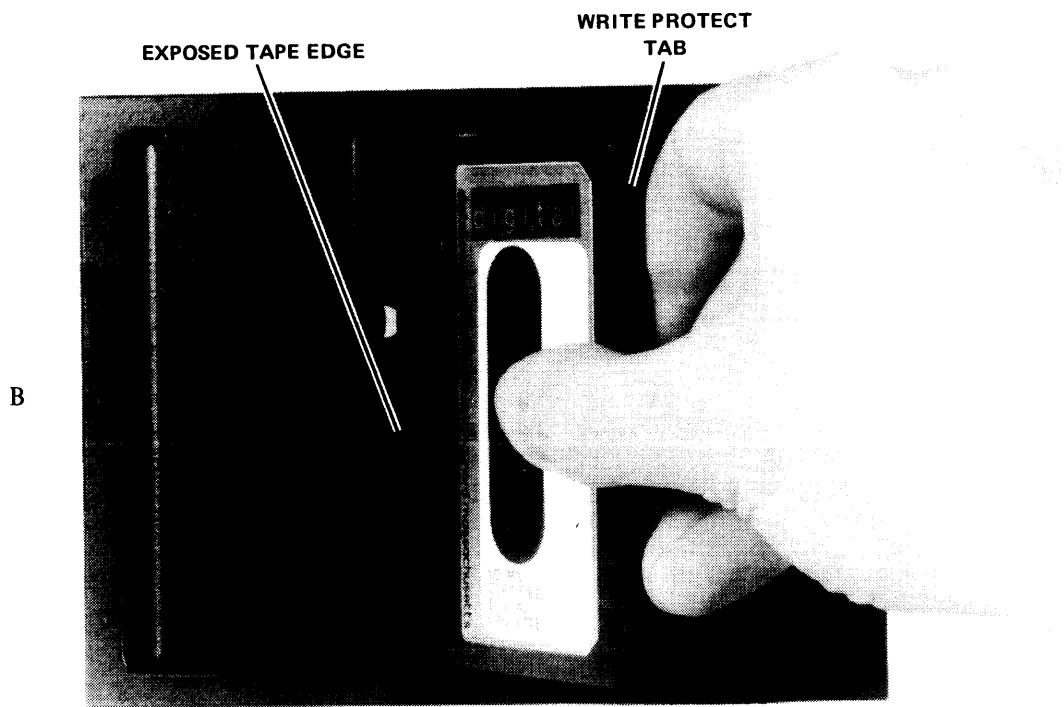

2. Hold the cassette with the thumb and index finger, and insert the cassette towards the left, at approximately a 45° angle, into the drive as indicated in Figure 2-2C. Ensure that the cassette label faces outward and that the exposed cassette tape edge is to the left of the drive sprockets.

3. Apply a leftward pressure, while simultaneously rotating the cassette inward onto the drive sprockets (Figure 2-2D). This action allows the cassette tape edge to slide under the lower door (lower door opens slightly) and bottom against the tape guides and read/write head.

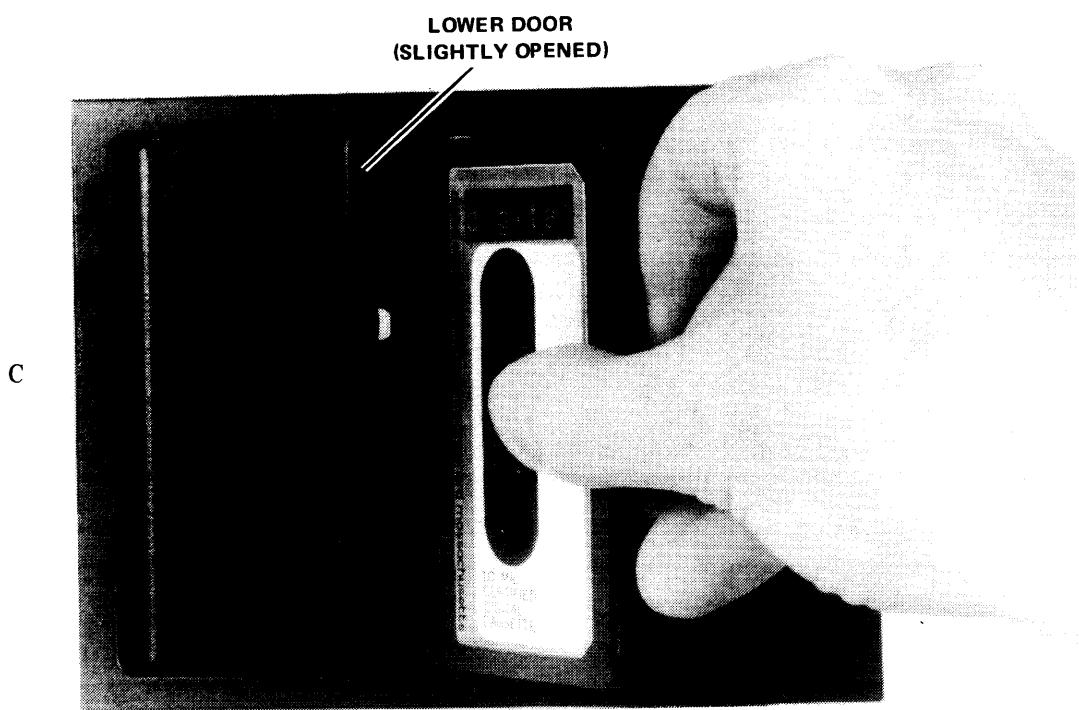

4. When the cassette is properly loaded, the locking bar automatically closes over the cassette back edge and the lower door closes flush with the drive frame (Figure 2-2E).

5. To remove the cassette, gently push the locking bar to the right until it detents and withdraw the cassette from the drive.

### 2.3.2 Normal Operating Procedure

1. Configure the cassette write protect tab for the desired operation and load the cassette (Paragraph 2.3.1).

2. Ensure that the Power-On toggle switch (located on the chassis rear panel) is in the ON position.

3. Press the manual REWIND pushbutton.

6746-7

Figure 2-2 Cassette Loading Sequence

6746-3

6746-3

Figure 2-2 Cassette Loading Sequence (Cont)

D

E

Figure 2-2 Cassette Loading Sequence (Cont)

# CHAPTER 3

## I/O INTERFACE SIGNALS

The TU60 DECassette Tape Transport interface is unique in that the transport does not utilize a separate controller. All the logic and circuit components necessary for data formatting, error checking, and cassette housekeeping are contained on two logic modules within the transport chassis; while the associated processor contains an interface module that converts the processor codes into commands and transmits them to the TU60. In addition, the interface module is capable of interpreting status flags received from the TU60, as well as temporary storage of input/output data.

There are several interface signals that must be present at the TU60 during an entire operation. These signals are SELECT ENABLE L, DRIVE B L, BACK BLOCK GAP L, BACK FILE GAP L, and R/W FILE GAP. The REWIND L, R/W CRC L, TRANSFER L, and WRITE MODE L signals, however, are transmitted and then stored in the TU60. All interface signals are at ground (low) for a logical 1 and +3V (high) for a logical 0. The following paragraphs describe the functional operation of each interface signal.

### 3.1 INPUT INTERFACE SIGNALS

#### 3.1.1 Select Enable L

This signal, at a logical 1, enables the TU60 input/output transmitters and receivers.

#### 3.1.2 Drive B L

This signal selects one of the dual tape drives. A logical 1 selects drive B or a logical 0 selects drive A.

#### 3.1.3 Start L

This signal, at a logical 1, is used in conjunction with a specific command to initiate command execution. If a command is to be performed, the drive must be in the ready state (READY L present) and the command present and stable one microsecond prior to START L. If this is the case, when START L is received, the TU60 electronics removes the READY L signal and initiates command execution. When READY L is removed, the interface then removes START L and while the command is being executed, any additional START L signals are ignored by the drive.

#### 3.1.4 Rewind L

This motion command signal, at a logical 1, is clocked by the START L signal to trigger the Rewind one-shot and thus cause a high speed (100–150 ips) tape rewind on the selected drive, to the beginning of the tape.

#### 3.1.5 Back Block Gap L

This motion command signal, at a logical 1, is clocked by the START L signal to cause reverse tape motion at read/write speed across a data block to the preceding pre gap.

#### 3.1.6 Back File Gap L

This motion command signal, at a logical 1, is clocked by the START L signal to cause reverse tape motion at search speed across a data file, stopping at two-thirds of the preceding file gap.

### 3.1.7 R/W File Gap L

This signal, at a logical 1, is used in conjunction with the WRITE MODE L signal to initiate either forward tape motion or a write file gap operation. If WRITE MODE L is a logical 1 when this signal is clocked by the START L signal, 535 ms of tape is erased; 1.4 seconds of tape is erased if at BOT. If WRITE MODE L is a logical 0 when this signal is clocked, tape on the selected drive moves forward, stopping two thirds into the next file gap.

### 3.1.8 Write Mode L

This signal selects either the read or write logic. For a write or write file gap operation, this signal, at a logical 1, is clocked by the START L signal to set the Write flip-flop.

For a read operation, this signal, at a logical 0, allows the START L signal to reset the Write flip-flop. Once the specific operation is initiated, the Write flip-flop remains either set or reset until the next operation is started.

### 3.1.9 Transfer L

During a write operation, this signal, at a logical 1, is transmitted to the TU60 in response to a TRANSFER REQ L signal. If this is the case, TRANSFER L sets the Trans Req flip-flop and the 8-bit byte is loaded into the TU60 Data Buffer.

During a read operation, this signal, at a logical 1, is transmitted to the TU60 in response to a TRANSFER REQ L signal. If this is the case, TRANSFER L sets the Trans Req flip-flop to indicate that the 8-bit byte has been loaded into the Interface Buffer.

### 3.1.10 R/W CRC L

During a write operation, this signal, at a logical 1, causes the accumulated CRC character to be recorded on the tape. R/W CRC L is transmitted to the TU60 while the final data byte is being recorded. When this occurs, the next TRANSFER REQ L signal is inhibited and the CRC character is recorded after the final data bit is written.

During a read operation, this signal, at a logical 1, tests the CRC Register for an error. At the start of a read operation, the CRC Err flip-flop is set and remains set while the data block is being read. After the first 8 CRC bits have been read, the interface transmits R/W CRC L. When the final TRANSFER REQ L signal is generated, the CRC Register is checked for zero. If the register is not zero (data read incorrectly), the CRC Err flip-flop remains set and, when READY L is generated, a CRC ERROR L signal is also generated. If the data has been read correctly, the CRC Err flip-flop resets and a CRC ERROR L signal is not generated.

### 3.1.11 Initialize L

This signal, at a logical 1, removes all flags (except EOT), generates READY L and, except for a rewind operation, stops tape motion regardless of the tape position.

## 3.2 OUTPUT INTERFACE SIGNALS

### 3.2.1 Off Line L

This signal, at a logical 1, indicates that the appropriate tape cassette is not properly loaded on the selected drive; or that the clear leader sensing lamp has failed.

### 3.2.2 Ready L

This signal, at a logical 1, indicates that the appropriate tape cassette has been properly loaded and tape motion is not occurring on the selected drive. In general, READY L is generated when all command functions have been completed and the drive is ready for the next operation; or when a clear leader is encountered.

### 3.2.3 End File L

This signal, at a logical 1, indicates that a file gap has been detected or the ensuing tape is blank.

### 3.2.4 EOT/BOT L (End Tape)

This signal, at a logical 1, indicates that the drive has reached the end-of-tape or beginning-of-tape (clear leader photosensor uncovered). When this occurs, tape motion stops and the READY L and EOT/BOT L signals are generated. EOT/BOT L is suppressed during a rewind operation or if the drive is not in the ready state.

### 3.2.5 Rewind L

This signal, at a logical 1, indicates that the selected drive is performing a rewind operation.

### 3.2.6 Write Protect L

This signal, at a logical 1, indicates that a write protected cassette is loaded on the selected drive, or that the drive is empty. If the cassette is write protected, the selected drive will not perform any write operations.

### 3.2.7 Write Status L

This signal, at a logical 1, indicates that a write or write file gap operation is being performed on the selected drive.

### 3.2.8 Transfer Req L

During a write operation, this signal, at a logical 1, indicates that the drive is ready to receive an 8-bit byte from the Interface Buffer. The TRANSFER REQ L signal is generated one bit time before a byte is needed and this signal is removed when the interface responds with a TRANSFER L signal.

During a read operation, this signal, at a logical 1, indicates that a byte from the drive is ready to be transferred to the Interface Buffer. The interface must then respond with a TRANSFER L signal, within one bit time ( $\approx 220 \mu s$ ) after the TRANSFER REQ L signal is generated or a time error occurs.

### 3.2.9 Time Error L

This signal, at a logical 1, indicates that the interface has not responded to a TRANSFER REQ L signal within the allotted time ( $\approx 220 \mu s$ ).

#### NOTE

The processor interface contains a one byte Data Buffer which allows the program the full byte time (1.8 ms) to respond to the TRANSFER REQ L.

### 3.2.10 CRC Error L

This signal, at a logical 1, indicates that a CRC error has occurred during a read operation. At the start of the read operation, the CRC Err flip-flop is set. When the final CRC character is read, the CRC Register is then checked for zero. If the register is not zero, the CRC Err flip-flop remains set and when READY L is generated, a CRC ERROR L signal is also generated.

### 3.2.11 PWR OK L

This signal, at a logical 1, indicates that the +5V power supply is operating normally.

### 3.2.12 R/W Bits 1–8 (Bi-directional)

These eight lines transmit data to and from the TU60 Data Buffer.

# CHAPTER 4

## THEORY OF OPERATION

### 4.1 GENERAL

Since the TU60 DECassette Tape Transport is a dual system, each drive has identical and separate motor control and servo logic. However, the selection, formatting, and read/write logic is common to both drives. It is therefore not possible to read or write from both drives simultaneously, but it is possible to perform a read or write operation on the selected drive and rewind the other drive concurrently.

Figure A-1 illustrates the major functional areas and associated signals of the TU60 Tape Transport, while this chapter only describes (in two distinct levels of detail) the logical operation of drive A. Once selected, drive B operates in an identical manner as drive A and is therefore not described. Paragraphs 4.2 and 4.3 briefly describe the over-all function of each operation that drive A can perform and Paragraph 4.5 describes these same operations in detail. Since the descriptions in Paragraph 4.5 refer to key elements and signals on the logic drawings in Appendix A, it is imperative that these drawings be used in conjunction with the text for a comprehensive understanding of each operation.

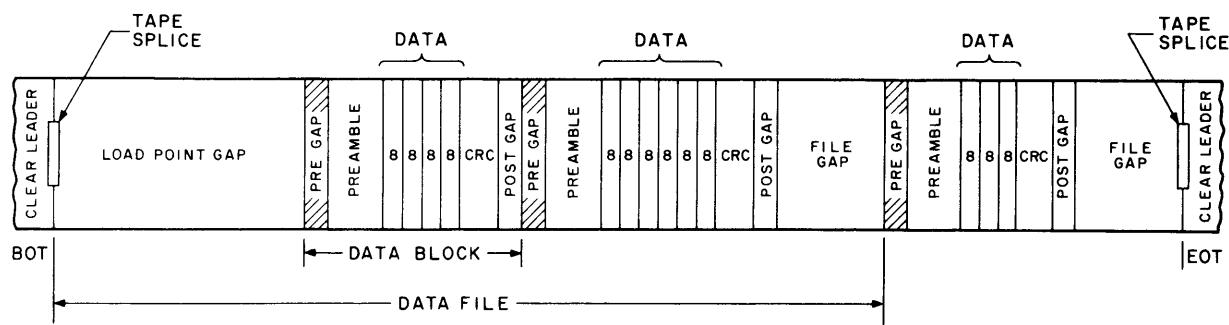

### 4.2 TAPE FORMAT AND MOTION CONTROL OPERATIONS

Figure 4-1 illustrates a typical TU60 data tape. The following paragraphs explain a specific command or manual control operation relative to the tape format. Before a command can be executed, however, one of the dual drives must first be selected and ready. (Refer to Paragraph 4.5.1 for a detailed description of the drive selection process.)

Figure 4-1 Typical Tape Format

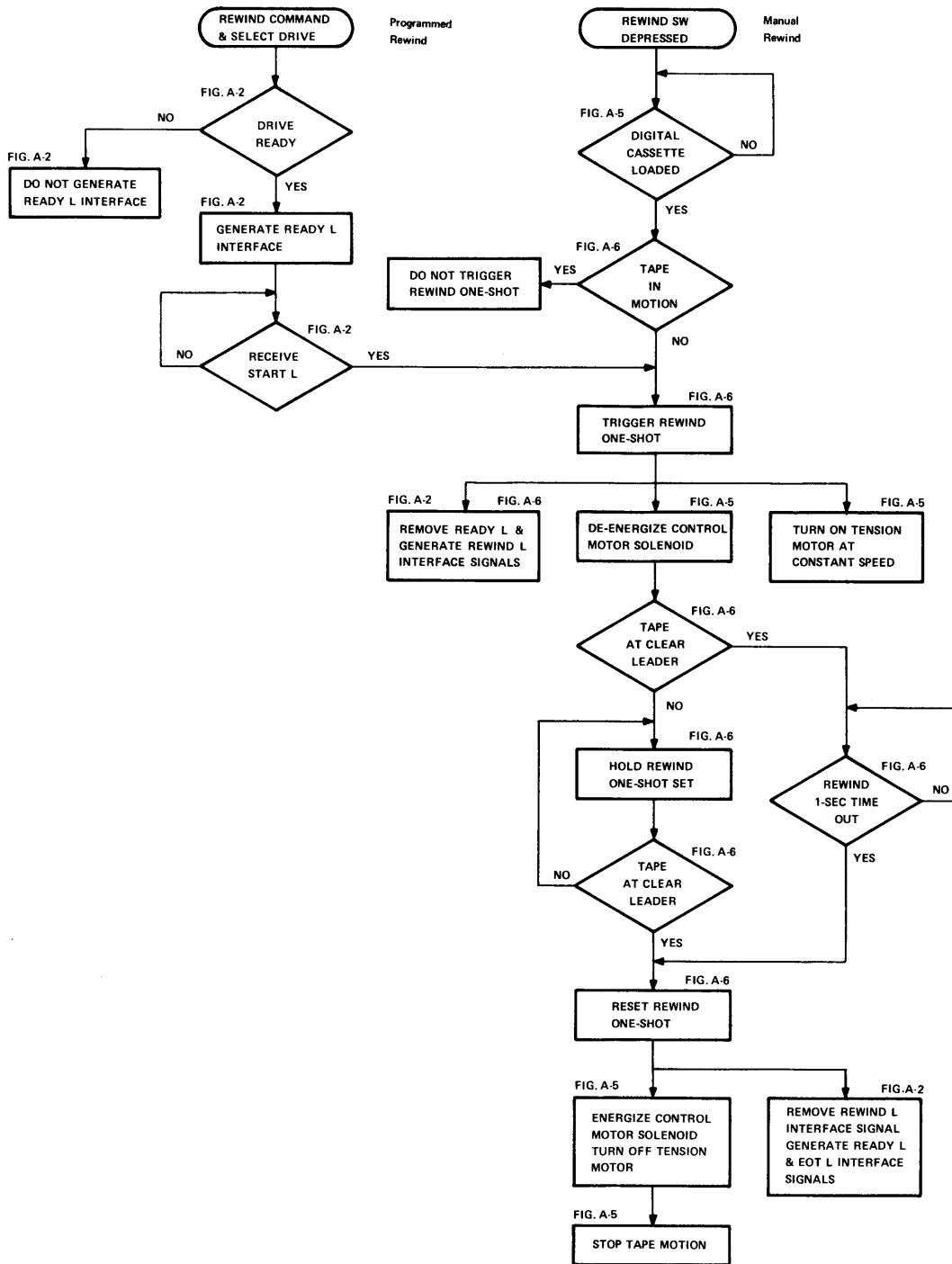

#### 4.2.1 Manual Rewind

To perform a manual rewind operation, the following conditions must be true:

- a. the appropriate cassette is properly loaded

- b. tape is not moving under program control.

Pressing the REWIND pushbutton when the preceding conditions are true sets the Rewind one-shot. If the tape is not at the beginning-of-tape (BOT) clear leader, the Rewind one-shot is held set even though the switch is released, allowing the tape to rewind completely at high speed (100–150 ips) to the BOT clear leader. If the tape is at the BOT clear leader when the REWIND pushbutton is pressed, the Rewind one-shot is set but is not held set and it times out one second later. Thus when the tape is at the BOT clear leader, backward tape motion occurs for less than one second.

Figure 4-2 illustrates the logical sequence during a manual rewind operation. Refer to Paragraph 4.5.2.1 for a detailed logic description of the preceding events.

#### 4.2.2 Programmed Rewind

To perform a program controlled rewind operation, the interface issues a Rewind command. If the appropriate cassette has been properly loaded and the tape is not already in motion, then the READY L interface signal is present at the interface. With READY L present, the interface then transmits the program generated START L signal, which clocks the Rewind command to set the Rewind one-shot. The remainder of the program controlled rewind operation is the same as a manual rewind operation.

Figure 4-2 illustrates the logical sequence during a program controlled rewind operation. Refer to Paragraph 4.5.2.2 for a detailed logic description of the preceding events.

#### 4.2.3 Back Block Gap

To space the tape backward one block (Figure 4-6), the interface issues a Back Block Gap (BBG) command. If the appropriate cassette has been properly loaded and the tape is not already in motion, then the READY L interface signal is present at the interface. With READY L present, the interface then transmits the program generated START L signal. If the tape is at the beginning-of-tape (BOT) clear leader, the signal INHIBIT H prevents reverse tape motion from occurring. If the tape is not at the BOT leader, reverse tape motion at read/write speed (9 ips average) occurs across an entire data block. When the tape is positioned at the preceding pre gap, the READY L interface signal is again generated and tape motion ramps to a stop.

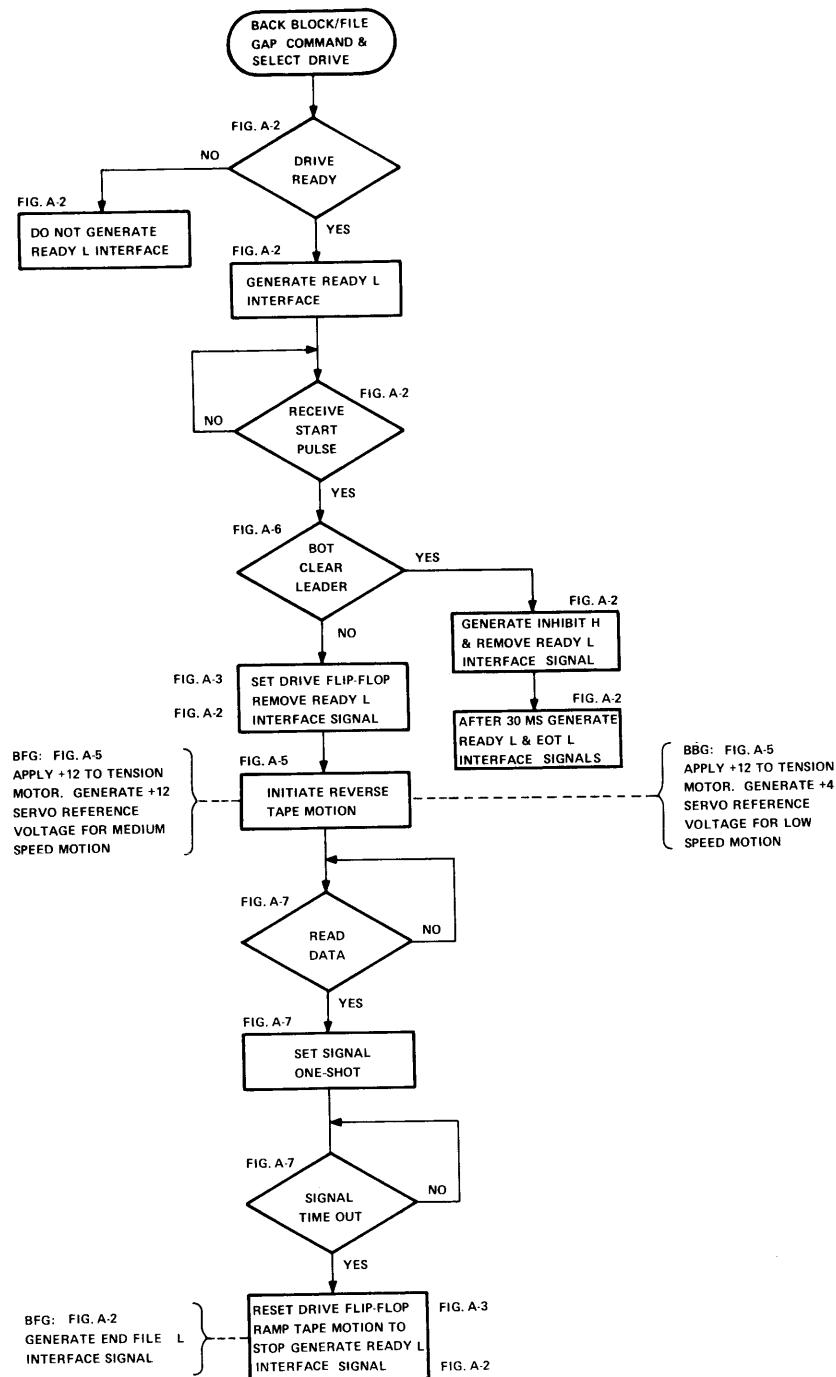

Figure 4-3 illustrates the logical sequence during a back block operation. Refer to Paragraph 4.5.3 for a detailed logic description of the preceding events.

#### 4.2.4 Back File Gap

A back file gap (BFG) operation is similar to the back block operation except that tape motion at search speed (22 ips average) occurs across a data file (Figure 4-6), stopping at two-thirds of the preceding file gap.

Figure 4-3 illustrates the logical sequence during a back file operation. Refer to Paragraph 4.5.4 for a detailed logic description of the preceding events.

Figure 4-2 Rewind Flow Chart

CP-0392

Figure 4-3 Back Block/File Gap Flow Chart

#### 4.2.5 Forward File Gap

A forward file gap (FFG) operation differs from the other motion control operations in that forward tape motion starts at read/write speed (9 ips average), then switches to search speed (22 ips average) if data is detected before a file gap.

If the tape is at the BOT when this command is issued (Figure 4-6), forward tape motion occurs at read/write speed across the load point gap, then switches to search speed when the first data block is detected. Tape motion continues at search speed, stopping at two-thirds of the following file gap. If the tape is stopped in the post gap prior to a file gap when this command is issued, forward tape motion occurs at read/write speed for 385 milliseconds, then tape motion stops at two-thirds of the same file gap. If tape is stopped at two-thirds of the file gap or at a block gap when this command is issued, forward tape motion starts at read/write speed, but switches to search speed when data is detected. When this occurs, the tape continues to move at search speed across the entire data file, stopping at two-thirds of the following file gap. Refer to Paragraph 4.5.6 for a detailed logic description of the preceding events.

### 4.3 READ/WRITE OPERATIONS

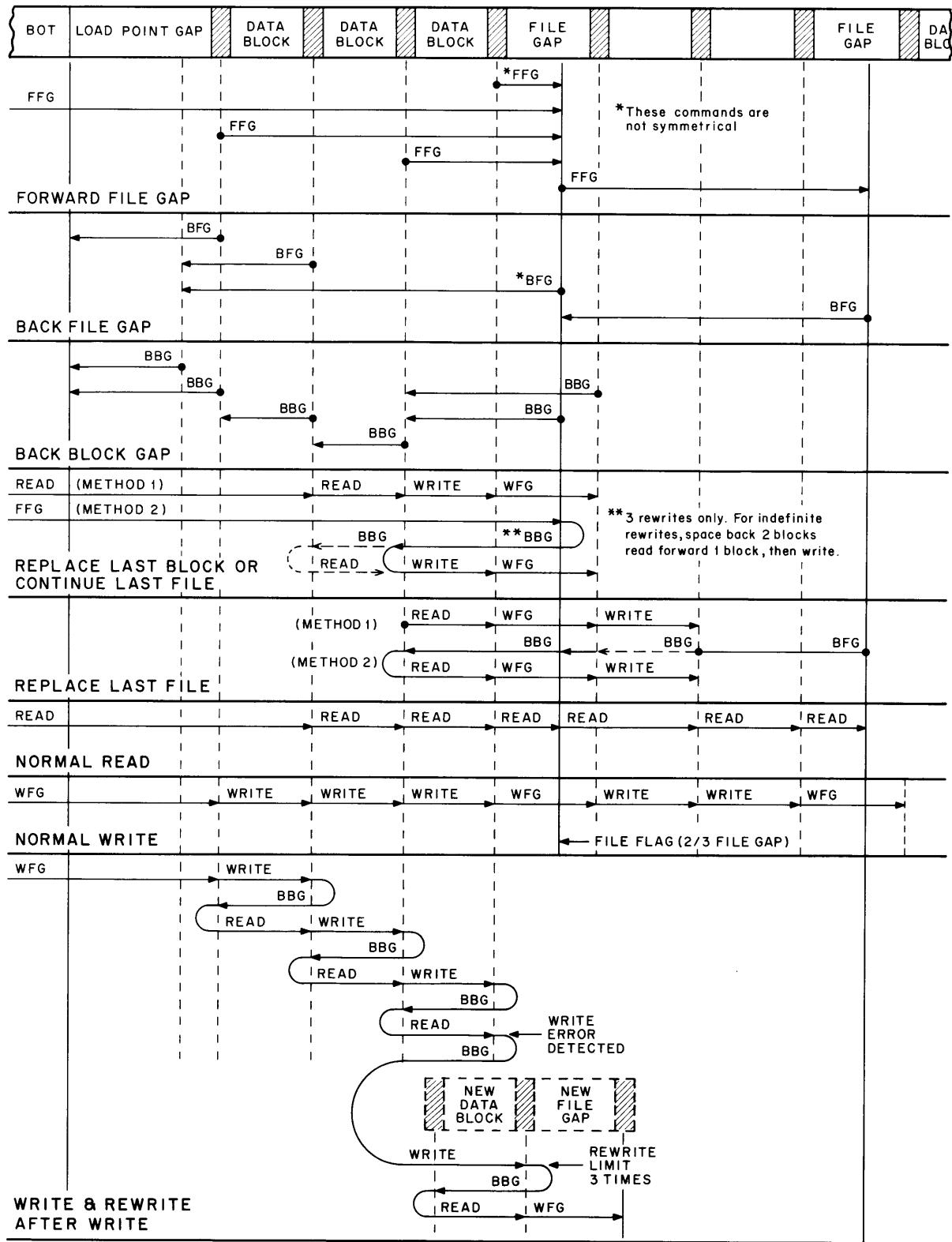

#### 4.3.1 Write File Gap

For certain specific programming operations, it may be advantageous to group consecutive data blocks together as a unit. This is accomplished by generating relatively long portions of erased tape (file gaps) before and after the data block group (Figure 4-1). Except for the available tape length, there is no limit to the number of files that may be contained on a single cassette.

To write a file gap, the interface simultaneously selects drive A (Paragraph 4.5.1), issues a Read/Write Gap command, and transmits the WRITE MODE L interface signal. If the cassette is write enabled and the drive is in the ready state, READY L is present at the interface. With READY L present, the interface then transmits the program generated START L signal to initiate forward tape motion at read/write speed (9 ips average). As the tape moves across the read/write head, the drive write circuits erase tape for 535 milliseconds. However, if the tape is at BOT when this command is issued, a 1.4 second load point gap is erased. Refer to Paragraph 4.5.7 for a detailed logic description of the preceding events.

#### NOTE

It is possible to perform concurrent write file gap operations; however, during forward file gap operations, two consecutive file gaps cause unspecified transport operation (may read as either 2 or 3 file gaps).

#### 4.3.2 Write Data Block

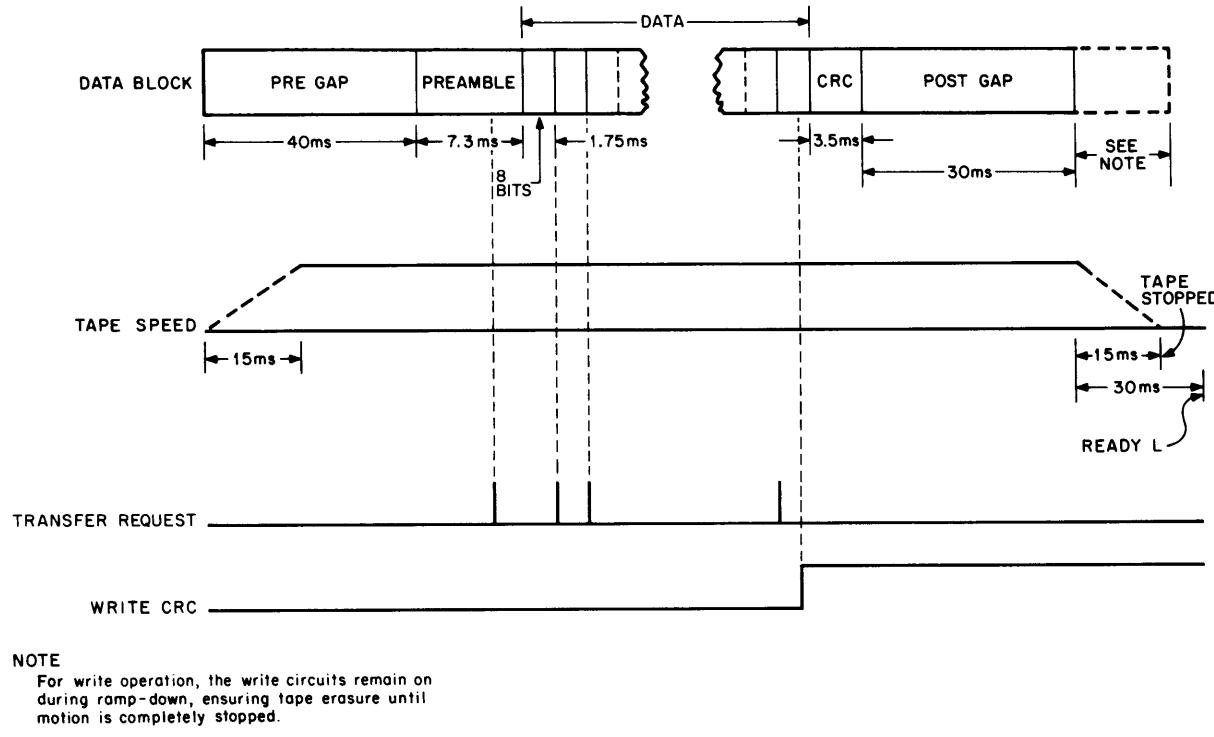

To write a block of data (Figure 4-4), the interface simultaneously selects drive A and issues a Write command. If the drive is in the ready state, READY L is present at the interface. With READY L present, the interface then transmits the program generated START L signal to initiate forward tape motion at read/write speed (9 ips average). As the tape moves across the read/write head, the write circuits erase a 40 millisecond pre gap prior to automatically recording the preamble (thirty-two logical 0s and one logical 1).

At approximately two-thirds of the preamble write time, the drive logic issues a Transfer Request signal which allows the interface to parallel transfer the first 8-bit byte into the Data Buffer, where it is stored until after the last preamble bit is written. When the last preamble bit is written, the first data bit is serially shifted out of the Data Buffer, phase encoded, and then written onto the tape. The remaining data bits are likewise shifted, phase encoded, and placed on the tape. Simultaneously, the data bits are also applied to a 16-bit Cyclic Redundancy Check (CRC) Register, where they are accumulated into a CRC character (Paragraph 4.5.10). When the eighth bit of the data byte is written, another Transfer Request is issued and the second 8-bit data byte is parallel transferred from the interface, temporarily stored in the Data Buffer, and then shifted out onto the tape.

This process continues until all the data bytes have been transferred, at which time, the interface issues a Write CRC command. When the last data bit is written on the tape, the 16-bit CRC character is then shifted from the CRC Register, phase encoded, and written on the tape. At the completion of the CRC write operation, a 30-millisecond post gap is erased and tape motion ramps to a stop. Fifteen milliseconds after the tape has completely stopped, READY L is again generated. (Refer to Paragraph 4.5.8 for a detailed logic description of the preceding events.)

Figure 4-4 Write Data Block

#### 4.3.3 Read Data Block/File

To read a block of data (Figure 4-4), the interface selects drive A and negates the WRITE MODE L signal. If the drive is in the ready state, READY L is present at the interface. With READY L present, the interface then transmits the program generated START L signal to initiate forward tape motion at read/write speed (9 ips average).

As the tape moves across the read/write head, preamble bits are detected. Approximately the first 24 preamble bits synchronize the read clock with the preamble bit frequency from the tape. Detection of the preamble frame bit (only logical 1 bit of the preamble) configures the drive logic to the data mode and allows the succeeding data bits to be serially shifted into the Data Buffer and also to be manipulated in the CRC Register (Paragraph 4.5.10). As the eighth bit of the first data byte is shifted into the Data Buffer, a Transfer Request signal is transmitted to the interface. The interface then stores the data byte from the eight interface lines in the Interface Buffer and responds with a Transfer signal. The second data byte is then likewise serially shifted into the Data Buffer and parallel transferred to the interface.

This process continues until all the data bytes plus the first eight bits of the CRC character have been transferred. At this time, the interface issues a Read CRC command. This command is stored in the drive logic and when the final CRC bit (16th CRC bit) is shifted into the Data Buffer, the CRC Register is tested for zero. The result of the CRC test is stored in the drive logic until the tape moves into the post gap. If the CRC Register was not zero when checked, the CRC ERROR L and READY L interface signals are generated and tape motion ramps to a stop. (Refer to Paragraph 4.5.9 for a detailed logic description of the preceding events.)

To read a data file, the interface simply selects drive A and transmits a program generated START L signal in response to every READY L signal received. If a file gap is detected while tape is being read, the END FILE L interface signal is also generated. Thus, a data file is read by successive read data block operations.

#### 4.4 PROGRAMMING RESTRICTIONS AND COMMAND TOPOLOGY

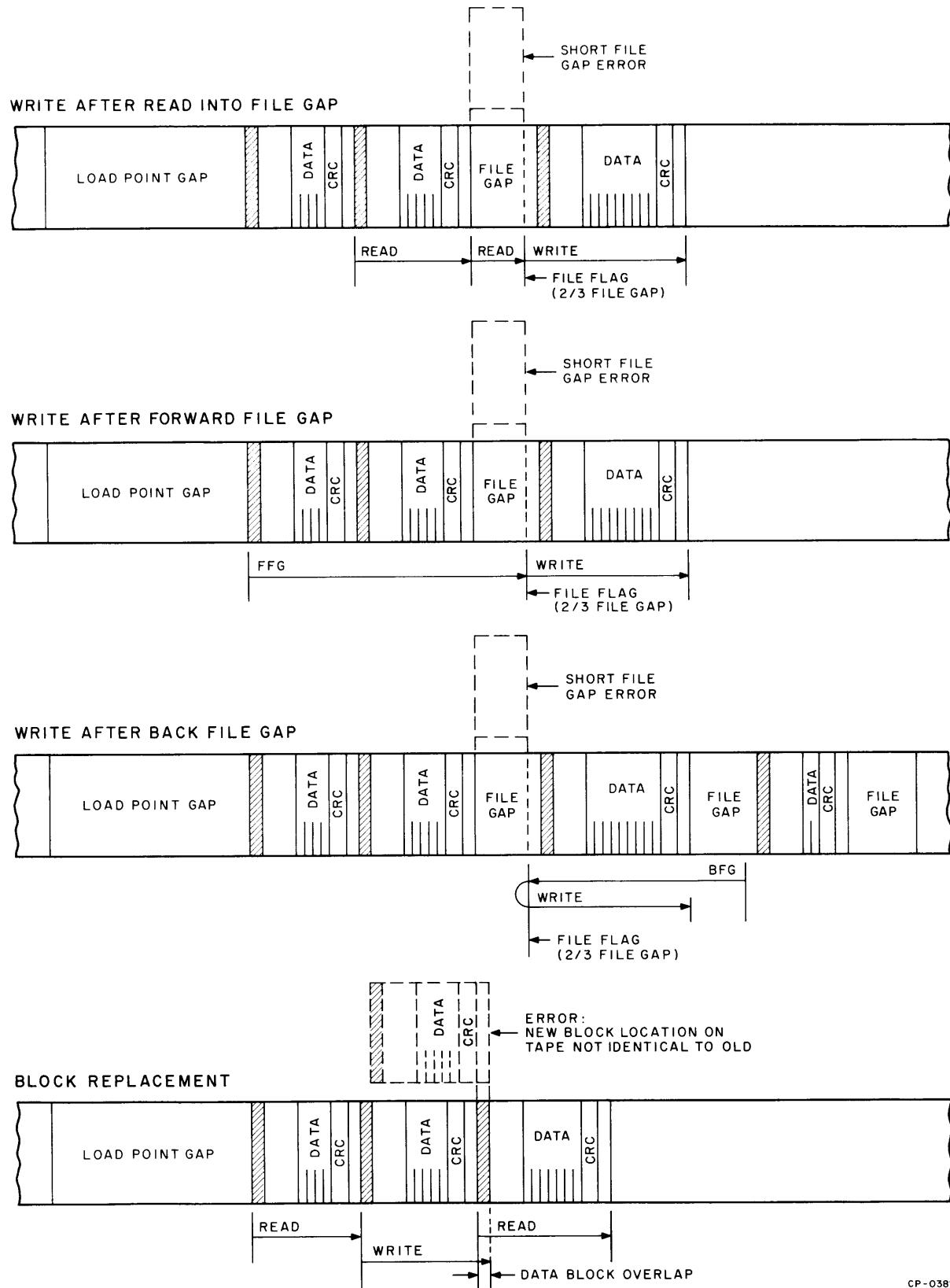

Although all data block formatting, error checking, and cassette housekeeping are hardware controlled within the TU60, tape formatting is software controlled. For this reason, certain command sequences are illegal and if attempted, these sequences will produce error conditions or unreadable tape. Figure 4-5 illustrates some of the illegal command sequences and the resultant tape motion. The complete list of illegal sequences is as follows:

- Write then FFG or Read

- Rewind then Write

- WFG then Read or FFG

- FFG then Write

- BBG then rewrite the same block more than 3 times

- BFG then Write

- Read into file gap then Write

In addition, commands that attempt reverse motion at the BOT or forward motion at the EOT do not initiate tape motion; however, thirty milliseconds after the commands are issued, READY L and EOT/BOT L are generated. If the cassette has just been loaded and a BBG or BFG is attempted, the TU60 does not respond and the command hangs up. To properly recover from this error condition, Initialize the processor, then perform a rewind.

Figure 4-6 illustrates the normal command operation.

#### NOTE

Since the tape motion commands are not symmetrical and the tape velocity varies slightly from transport to transport, these commands should not be used in an attempt to replace an individual data block (other than the last block on the tape).

#### 4.5 DETAILED LOGIC DESCRIPTIONS

The following paragraphs describe the detailed logical operation of drive A. Once selected, drive B operates in an identical manner as drive A and is therefore not described. Since the logical descriptions in these paragraphs are rather complex, it is suggested that the reader become familiar with the specific operation by referring to the simplified descriptions in Paragraphs 4.2 and 4.3 prior to reading these detailed descriptions.

##### 4.5.1 Drive Selection

To perform any program controlled operation, a particular drive must first be selected. To accomplish this, the interface generates the SELECT ENABLE L and DRIVE B L (high for drive A, low for drive B selection) interface signals.

Figure 4-5 Illegal Command Sequence

CP - 0382

Figure 4-6 Command Topology

SELECT ENABLE L, applied to the transport interface logic (Figure A-2), enables one leg of all but the CRC and EOT/BOT output line transmitters. In addition, SELECT ENABLE L, applied through an inverter, enables one leg of all but the GO and INIT input line receivers. DRIVE B L (high), when applied to the interface logic, produces the signal DRIVE A L which, when applied to the read/write and servo logic (Figure A-7), produces the signal SEL A H/SEL B L. This internal control signal allows drive A to perform the various control and read/write operations.

#### 4.5.2 Rewind

A rewind operation can be performed manually or under program control. The following paragraphs describe both rewind methods.

**4.5.2.1 Manual Rewind** – Pressing the REWIND pushbutton on the drive front panel generates the signal MANUAL REWIND A H (Figure A-6). If the appropriate tape cassette has been properly loaded, the CAS LOAD A switches (Figure A-5) are configured as shown to produce the signal LOADED A H. (Refer to Paragraph 1.4.2 for a description of the CAS LOAD microswitch operation.) LOADED A H, ANDed with REWIND A L (high if the drive is not already performing a rewind operation), produces the signal READY A L. If the tape is not in motion under program control, MOVE A H (Figure A-6) is low. This signal, applied through an inverter, is ANDed with MANUAL REWIND A H to trigger the 1-second Rewind one-shot.

With the Rewind one-shot set, REWIND A H, applied through the write protect switch, produces the signal WRITE PERMIT H (low). This signal, when applied to the read/write logic (Figure A-7), produces WRITE ENABLE H (low) to disable the write drivers and prevent a tape erasure during the rewind operation. REWIND A L, applied through a NAND gate (Figure A-6), is then ANDed with LDR A L (high if the tape is not at clear leader) to hold the one-shot set even though the switch is no longer depressed. In addition, REWIND A L, applied to the read/write and servo logic (Figure A-5), causes READY A L to come high and de-energize the Control Motor Solenoid (SOL A). This action allows the solenoid spring to move the control motor away from the rubber wheel and thus permit the cassette lower reel to turn freely. Simultaneously, REWIND A H, ANDed with LOADED A H, turns on the tension motor at constant speed (Paragraph 4.6.2) to rewind the tape.

When the tape is completely rewound, the clear leader at the beginning of the tape uncovers the clear leader photosensor. This action generates the signal LEADER A H (Figure A-6) to reset the Rewind one-shot. When the Rewind one-shot resets, REWIND A H is removed from the read/write and servo logic (Figure A-5) stopping the tension motor; while READY A L energizes SOL A. Due to the motor speed and inertia, clear leader is wound past the corner roller of the cassette before the solenoid is engaged to completely stop the tape motion.

Pressing the REWIND pushbutton while the tape is at a clear leader triggers the Rewind one-shot to produce tape motion as previously described; however, since the tape is at a clear leader, LDR A L (Figure A-6) is low. If REWIND is pressed when the tape is at the BOT clear leader, tape moves backward until the 1-second Rewind one-shot times out then tape motion stops. If REWIND is pressed when the tape is at the EOT clear leader, tape moves backward; however, before the Rewind one-shot times out, the tape oxide has moved to cover the clear leader photosensor causing LDR A L to come high and hold the Rewind one-shot set. Hence, backward tape motion continues until the BOT clear leader is detected.

**4.5.2.2 Programmed Rewind** – To initiate a program controlled rewind operation, the interface simultaneously selects drive A (Paragraph 4.5.1) and issues a Rewind command. REWIND CMD L applied through the transport interface logic (Figure A-2) enables the bottom leg of the set gate on the Rewind flip-flop (Figure A-6). If the appropriate tape cassette has been properly loaded, the CAS LOAD A switches (Figure A-5) are configured as shown to produce the signal LOADED A H. (Refer to Paragraph 1.4.2 for a description of the CAS LOAD microswitch operation.) LOADED A H, ANDed with SEL A H (Figure A-6), generates the signal DRIVE EMPTY H (low) which removes the OFF LINE L interface signal (Figure A-2). If the tape is not already performing a rewind operation, REWIND H is low (Figure A-6) and DRIVE L is high (Figure A-2), producing the READY L interface signal.

At this point, the interface transmits the program generated START L signal, which ANDs with READY L (Figure A-2) to produce GO H. GO H, ANDed with REWIND CMD H (Figure A-6), triggers the 1-second Rewind one-shot. With the Rewind one-shot set, REWIND A H, applied through the write protect switch, produces the signal WRITE PERMIT H (low). This signal, when applied to the read/write logic (Figure A-7), produces WRITE ENABLE H (low) to disable the write drivers and prevent tape erasure during the rewind operation. REWIND A L, applied through a NAND gate (Figure A-6), is then ANDed with LDR A L (high if the tape is not at clear leader) to hold the one-shot set even though the command terminates. In addition, REWIND A L, applied to the read/write and servo logic (Figure A-5), causes READY A L to come high and de-energize the Control Motor Solenoid (SOL A). This action allows the solenoid spring to move the control motor away from the rubber wheel and thus permit the cassette lower reel to turn freely. Simultaneously, REWIND A H, ANDed with LOADED A H, turns on the tension motor at constant speed (Paragraph 4.6.2) to rewind the tape. While the tape is rewinding, REWIND H is applied to the transport interface logic (Figure A-2) to remove the READY L and generate the REWIND L interface signals.

When the tape is completely rewound, the clear leader at the beginning of the tape uncovers the clear leader photosensor. This action generates the signal LEADER A H (Figure A-6) to reset the Rewind one-shot. When the Rewind one-shot resets, REWIND A H is removed from the read/write and servo logic (Figure A-5) stopping the tension motor; while READY A L energizes SOL A. Due to the motor speed and inertia, clear leader is wound past the corner roller of the cassette before the solenoid is engaged to completely stop the tape motion.

#### 4.5.3 Back Block Gap

To space the tape backward one block, the interface simultaneously selects drive A (Paragraph 4.5.1) and issues a Back Block Gap command. BACK BLOCK GAP L, applied through the transport interface logic (Figure A-2), produces the signal REV L. REV L is then applied through an inverter (Figure A-5) to enable the top leg of the drag motor control gate, and the bottom leg of the servo input gate. If the tape is not in motion, the Drive flip-flop (Figure A-3) is in the reset state, producing the signal DRIVE L (high) which, when applied to the transport interface logic (Figure A-2), generates the READY L interface signal.

At this point, the interface transmits the program generated START L signal, which ANDs with READY L (Figure A-2) to reset the Write flip-flop. If the tape is at the beginning-of-tape (BOT) clear leader when START L is issued, and the previous command was a reverse command, the Inhibit gating circuit produces the signal INHIBIT H. INHIBIT H, applied to the bottom leg of a NAND gate, prevents D GO L from being generated and thus, reverse tape motion onto the BOT leader is prevented. In addition, INHIBIT H allows the resultant signal from START L to trigger the 30-millisecond Stop Delay one-shot. This action removes the READY L interface signal. When the Stop Delay one-shot times out, READY L is again generated, along with the EOT/BOT L interface signal to indicate a fault condition. If the tape is not at the (BOT) clear leader, INHIBIT H is not produced, resulting in the signal D GO L. This signal sets the Drive flip-flop (Figure A-3), generating DRIVE L. DRIVE L removes the READY L interface signal and enables the bottom leg of the MOVE A H gate (Figure A-5).

If the appropriate tape cassette has been properly loaded and drive A is selected, MOVE A H is generated. This signal is then ANDed with REV H at the tension motor control gate to apply +12 Vdc to the drag motor. In addition, MOVE A H is ANDed with REV H at the servo input gate to initiate reverse tape motion under servo control (Paragraph 4.6.1). Since a back block gap operation is being performed, HIGH SPEED H is low (Figure A-2). This signal, when applied through an inverter (Figure A-5), produces a +4 Vdc V REF signal. With +4 Vdc applied to the V REF terminal of the servo, reverse tape motion occurs at read/write speed (9 ips average).

As the tape moves backward across the read/write head, data from the tape triggers the Signal one-shot (Figure A-7). As long as data is present, the Signal one-shot remains set (Paragraph 4.5.9.3). 15 milliseconds after the last data transition is detected (tape in the pre gap), the Signal one-shot resets. This action removes SIGNAL H from the Drive flip-flop (Figure A-3), causing it to reset. With DRIVE L high, the MOVE A H gate (Figure A-5) is disabled, allowing tape motion to ramp to a stop. In addition, DRIVE L (high), applied to the transport interface logic (Figure A-2), generates the READY L interface signal.

#### 4.5.4 Back File Gap

To space the tape backward one file, the interface simultaneously selects drive A (Paragraph 4.5.1) and issues a Back File Gap command. BACK FILE GAP L, applied through the transport interface logic (Figure A-2), produces the signals REV L and HIGH SPEED H. The program generated START L signal removes the READY L interface signal and conditions the tension and control motors exactly the same as for a back block gap operation (Paragraph 4.5.3). However, HIGH SPEED H, applied through an inverter (Figure A-5), produces a +12 Vdc V REF signal. In addition, HIGH SPEED H is applied to the switching circuit of the Signal one-shot (Figure A-7) to change the one-shot timeout to 75 milliseconds. With +12 Vdc applied to the V REF terminal of the servo (Figure A-5), reverse tape motion occurs at search speed (22 ips average).

The remainder of the back file gap operation is similar to the back block gap operation. However, because of the extended Signal one-shot timeout, reverse tape motion stops at two-thirds of the previous file gap (75 milliseconds after the last data transition is detected).

#### 4.5.5 Turn-Around Clear Leader Handling

If forward tape motion is occurring near the end of the tape, and any of the reverse commands (Rewind, BBG, or BFG) are issued, it is possible that before forward tape motion has stopped the tape may have coasted onto the end-of-tape clear leader. If this occurred, the signal LDR A L (Figure A-6) would cause one of the following erroneous operations:

- a. Immediately reset the Rewind one-shot, indicating that the tape has completely rewound to the beginning of the tape and is ready for forward operations.

- b. Immediately reset the Drive flip-flop, indicating that the beginning of the tape has been reached and the reverse tape operation is completed.

To prevent this, whenever tape is moving forward, the Dir A flip-flop is set. When the Rewind one-shot sets for a rewind operation (Paragraph 4.5.2), the signal REWIND A L resets the Dir A flip-flop. This action triggers the 125-millisecond LDR Inhibit one-shot to inhibit the signal LDR A L for 125 milliseconds during the tape turn-around time. Similarly, for all other reverse commands, REV L (high) resets the Dir A flip-flop to trigger LDR Inhibit.

#### 4.5.6 Forward File Gap

To space the tape forward one file, the interface simultaneously selects drive A (Paragraph 4.5.1) and issues a Read/Write Gap command.

##### NOTE

The Read/Write Gap command is used for both a forward file and a write file gap operation; however, for a forward file gap operation, the interface does not transmit WRITE MODE L.

R/W GAP L, applied through the transport interface logic (Figure A-2), generates the signal R/W GAP H. If the tape is not in motion, the Drive flip-flop (Figure A-3) is in the reset state, producing the signal DRIVE L (high) which, when applied to the transport interface logic (Figure A-2), generates the READY L interface signal.

At this point, the interface transmits the program generated START L signal, which ANDs with READY L (Figure A-2) to reset the Write flip-flop and also generate READ FG H. If the tape is at the end-of-tape (EOT) clear leader when START L is issued, and the previous command was a forward command, the Inhibit gating circuit produces the signal INHIBIT H. INHIBIT H, applied to the bottom leg of a NAND gate, prevents D GO L from being generated and thus, forward tape motion onto the EOT leader is prevented. In addition, INHIBIT H allows the resultant signal from START L to trigger the 30-millisecond Stop Delay one-shot. This action removes the READY

L interface signal. When the Stop Delay one-shot times out, READY L is again generated, along with the EOT/BOT L interface signal, to indicate a fault condition. If the tape is not at the EOT leader, INHIBIT H is not produced and the signal D GO L is generated. This signal sets the Drive flip-flop (Figure A-3), generating DRIVE L. DRIVE L removes the READY L interface signal and enables the bottom leg of the MOVE A H gate (Figure A-5). If the appropriate tape cassette has been properly loaded and drive A is selected, MOVE A H is generated. Since a forward file gap operation is being performed, REV L is high (Figure A-2) and HIGH SPEED H is low. REV L (high) is applied through an inverter (Figure A-5) to disable the tension motor control gate and thus apply +5 Vdc to the tension motor. In addition, REV L (high), ANDed with MOVE A H at the servo input gate, initiates forward tape motion under servo control (Paragraph 4.6.1). HIGH SPEED H (low), applied through an inverter, produces a +4 Vdc V REF signal. With +4 Vdc applied to the V REF terminal of the servo, forward tape motion occurs at read/write speed (9 ips average).

If the tape is at the beginning-of-tape (BOT) clear leader, the signal LDR H is present. LDR H, applied through an inverter (Figure A-3), disables the D input of the First LDR flip-flop. When D GO L is generated, this flip-flop resets, producing the signal FIRST LDR L. FIRST LDR L, applied through a NOR gate, holds the Tape Blank one-shot set, thus permitting tape motion across the first extended file gap.

If the tape is not at clear leader or data when the space command is received, READ FG H releases the 385-millisecond Tape Blank one-shot. If this one-shot times out before data is detected, BLANK STOP L is generated to reset the Drive and set the EOF flip-flops. DRIVE L (high) disables the MOVE A H gate (Figure A-5), allowing tape motion to ramp to a stop. In addition, DRIVE L (high) and END FILE H are applied to the transport interface logic (Figure A-2) to generate the READY L and END FILE L interface signals.

If, after tape motion is initiated, data is detected prior to the 385-millisecond Tape Blank timeout, the Signal one-shot is triggered (Figure A-7), generating SIGNAL H to set the First LDR flip-flop and also to keep the Tape Blank one-shot set. As long as data is present, the Signal one-shot remains set (Paragraph 4.5.9.3). SIGNAL H, applied to the interface logic (Figure A-2), produces HIGH SPEED H which, when applied through an inverter (Figure A-5), produces a +12 Vdc V REF signal to switch the tape servo system to search speed (22 ips average). In addition, HIGH SPEED H and R/W GAP H, applied to the switching circuits of the Signal one-shot, changes the one-shot timeout to 150 milliseconds. 150 milliseconds after the last data transition is detected (tape advanced to the next file gap), the Signal one-shot resets generating SIGNAL H (low). This signal resets the Drive and sets the EOF flip-flop (Figure A-5), producing the END FILE L interface signal and stopping tape motion two-thirds into the file gap.

#### 4.5.7 Write File Gap

To write a file gap, the interface simultaneously selects drive A (Paragraph 4.5.1), issues a Read/Write Gap command, and transmits the WRITE MODE L interface signal.

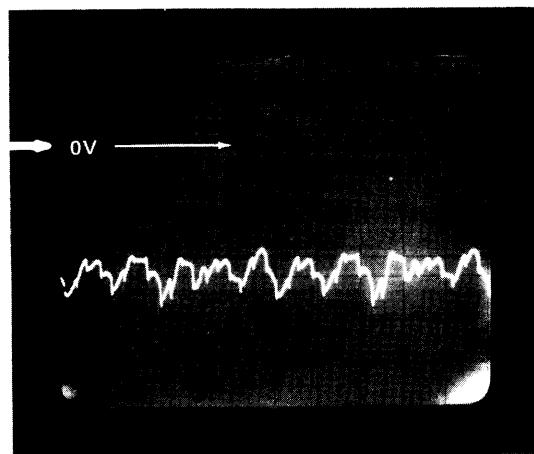

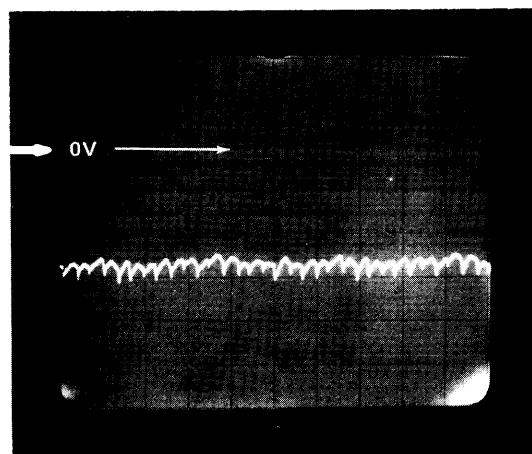

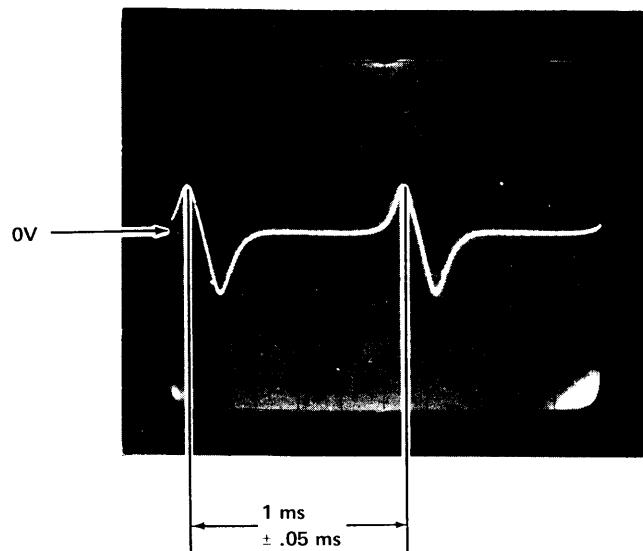

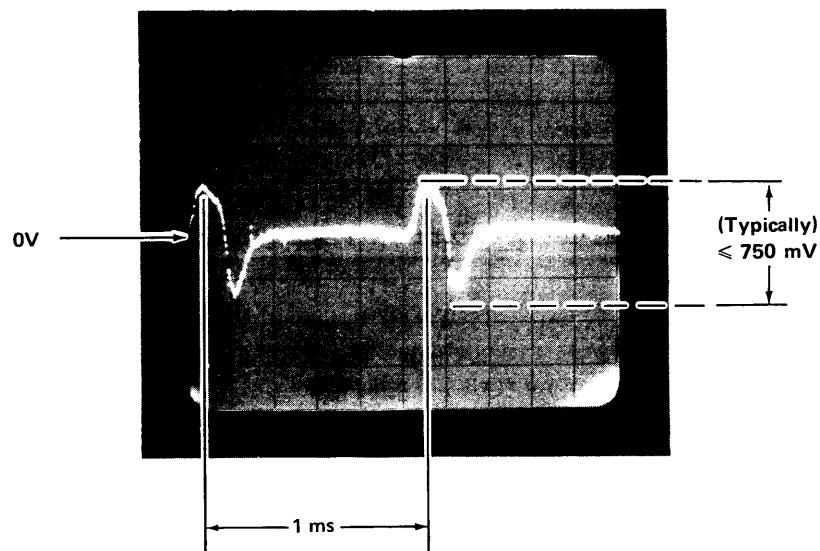

##### NOTE